CERN/LHCC 99–12 ALICE TDR 4 18 June 1999

# ALICE

# **Technical Design Report**

of the

**Inner Tracking System (ITS)**

This edition contains a few minor modifications, essentially corrections of typographical errors, relative to the first, limited, edition.

Cover page drawing: Perspective study of a chalice, by P. Uccello, painter of the Florentine Renaissance.

Cover design by Fabienne Marcastel

Printed at CERN June 1999

ISBN 92-9083-144-8

**Alessandria, Italy,** Facoltà di Scienze dell'Università: G. Dellacasa, L. Ramello, E. Scalas, M. Sitta and C. Soave.

Aligarh, India, Physics Department, Aligarh Muslim University: N. Ahmad, S. Ahmad, T. Ahmad, W. Baritak, M. Irfan and M. Zafar.

Athens, Greece, Nuclear and Particle Physics Division, University of Athens: A.L.S. Angelis, A. Kapogiannis, G. Mavromanolakis and A.D. Panagiotou.

**Athens, Greece,** Institute of Nuclear Physics, NRC Demokritos: K. Kalfas.

Bari, Italy, Dipartimento di Fisica dell'Università and Sezione INFN:

D. Cozza, G. De Cataldo, D. Dell'Olio, L. Dell'Olio, D. Di Bari, D. Elia, N. Facchini, R.A. Fini,

B. Ghidini, V. Lenti, L. Liberti, R. Loconsole, V. Manzari, E. Nappi<sup>1)</sup>, F. Navach, F. Posa and S. Stucchi.

**Bari, Italy,** Politecnico and Sezione INFN: F. Corsi, D. De Venuto, M. Di Ciano, R. Dinapoli, G. Gramegna, A. Grimaldi, P. Lamanna, C. Marzocca, G. Matarrese and E. Monno.

**Beijing, China,** China Institute of Atomic Energy: H. Guo, X. Li, S. Lu, Z. Lu, B. Sa, H. Wang, J. Zhou, S. Zhou and X. Zhu.

**Bergen, Norway,** Department of Physics, University of Bergen: H. Helstrup, A. Klovning, O.A. Maeland, O.H. Odland, D. Röhrich, R. Rongved and T.F. Thorsteinsen.

**Bhubaneswar, India,** Institute of Physics: A.K. Dubey, D.P. Mahapatra, B. Mohanty and S.C. Phatak.

**Birmingham, United Kingdom,** School of Physics and Space Research, University of Birmingham: I.J. Bloodworth, D. Evans, G.T. Jones, P. Jovanović, J.B. Kinson, A. Kirk, O. Villalobos Baillie and M.F. Votruba.

Bologna, Italy, University/INFN:

F. Anselmo, P. Antonioli, G. Bari, M. Basile, L. Bellagamba, D. Boscherini, L. Brocco, A. Bruni,

G. Bruni, G. Cara Romeo, D. Casadei, E. Cerron, F. Cindolo, N. Coppola, M. Corradi, S. De Pasquale,

D. Falchieri, A. Gabrielli, E. Gandolfi, P. Giusti, B. Guasina, D. Hatzifotiadou, N.Y. Kim, G. Laurenti,

M.L. Luvisetto, A. Margotti, T. Massam, A. Masetti, R. Nania, F. Palmonari, A. Pesci, F. Pierella,

A. Polini, G. Sartorelli, A. Semak, G. Valenti, M.C.S. Williams and A. Zichichi.

**Bratislava, Slovakia,** Faculty of Mathematics and Physics, Comenius University: J. Braciník, V. Černý, J. Ftáčnik, V. Hlinka, M. Ivanov, R. Janik, R. Lietava, M. Pikna, J. Pišút, N. Pišútová, B. Sitar, P. Strmeň and I. Szarka.

**Bucharest, Romania,** National Institute for Physics and Nuclear Engineering: A. Andronic, V. Catanescu, M. Ciobanu, M. Duma, D. Moisa, M. Petrovici, V. Simion, C. Staii and G. Stoicea. **Budapest, Hungary,** KFKI Research Institute for Particle and Nuclear Physics, Hungarian Academy of Sciences:

E. Denes, B. Eged, Z. Fodor, G. Harangozo, T. Kiss, G. Palla, G. Rubin, J. Sulyan, L. Szendrey, J. Sziklai, D.L. Tarjan, Z. Varga, B.N. Vissy and J. Zimanyi.

**Cagliari, Italy,** Dipartimento di Fisica dell'Università and Sezione INFN: C. Cicalo, A. De Falco, M.P. Macciotta-Serpi, A. Masoni, S. Mauro, G. Puddu, P. Randaccio, S. Serci, E. Siddi and G. Usai.

**Calcutta, India,** Saha Institute of Nuclear Physics: P. Bhattacharya, S. Bose, Sukalyan Chattopadhyay, N. Majumdar, A. Sanyal, S. Sarkar, P. Sen, S.K. Sen and B.C. Sinha.

**Calcutta, India,** Variable Energy Cyclotron Centre: Subhasis Chattopadhyay, M.R. Dutta Majumdar, M.S. Ganti, T.K. Nayak, R.N. Singaraju, Bikash Sinha, M.D. Trivedi and Y.P. Viyogi.

**Catania, Italy,** Dipartimento di Fisica dell'Università and Sezione INFN: A. Badalà, R. Barbera, U. Becciani, M. Gulino, S. Ingrassia, A. Insolia, F. Librizzi, L. Lo Nigro, D. Lo Presti, D. Nicotra, A. Palmeri, G.S. Pappalardo, L. Pappalardo, C. Petta, N. Randazzo, S. Reito, F. Riggi, G.V. Russo and M. Russo.

CERN, Switzerland, European Laboratory for Particle Physics:

J. Bächler, J.A. Belikov<sup>2)</sup>, V. Berejnoi<sup>3)</sup>, J.-C. Berset, R. Brun, M. Burns, M. Campbell, E. Cantatore, W. Carena, F. Carminati, P. Chochula, J. Christiansen, D. Collados, J. Cruz de Sousa Barbosa, M. Davenport, J. de Groot, A. Di Mauro, R. Divià, C. Eisenberg, C. Engster, J. Espirito Santo, M. Fageda, H.G. Fischer, M. Flammier, F. Formenti, D. Fraissard, E. Futo<sup>4)</sup>, E. Gaumann, B. Goret, T. Grassi<sup>5)</sup>, C. Gregory, M. Hoch, P.G. Innocenti, A. Jachołkowski, W. Klempt, A. Kluge, X. Lagrue, G. Lecoeur, J.C. Legrand, L. Leistam, P. Lenoir, Y. Lesenechal, C. Lourenço, P. Martinengo, M. Mast, T. Meyer, H. Milcent, R. Monnin, M. Morel, A. Morsch, M. Mota, L. Musa, B. Perrin, D. Picard, L. Pigni, F. Piuz, E. Quercigh, J. Raynaud, H. Renshall, A. Rivetti, K. Šafařík, J.-C. Santiard, J. Schukraft, E. Schyns, A. Sharma, W. Snoeys, P. Sonderegger, M. Spegel, D. Swoboda, P. Szymanski, G. Tabary, J. van Beelen, H. van der Velde, P. Vande Vyvre, A. Vascotto, D. Vranic, S. Wenig, P. Wertelaers, T. Williams and K. Zelazowski.

**Chandigarh, India,** Physics Department, Panjab University: M.M. Aggarwal, A.K. Bhatia, V.S. Bhatia, R. Chugh and V. Vashisht.

Clermont-Ferrand, France, Université Blaise Pascal and IN2P3:

J.P. Alard, A. Baldit, V. Barret, N. Bastid, G. Blanchard, J. Castor, T. Chambon, A. Cosquer, P. Crochet, F. Daudon, A. Devaux, P. Dupieux, B. Espagnon, J. Fargeix, P. Force, L. Lamoine, F. Manso, G. Roche, O. Roig, L. Royer and P. Saturnini.

**Coimbra, Portugal,** Departamento de Física, Faculdade de Ciências e Tecnologia: R. Ferreira Marques, P. Fonte<sup>1)</sup> and A. Policarpo.

**Columbus, U.S.A.,** Department of Physics, Ohio State University: T.J. Humanic, M. Lisa, G. Lo Curto, B.S. Nilsen, G. Paić, D.M. Reichhold and E. Sugarbaker.

Copenhagen, Denmark, Niels Bohr Institute:

I. Bearden, H. Bøggild, J. Gaardhøje and B. Nielsen.

**Cracow, Poland,** Henryk Niewodniczanski Institute of Nuclear Physics, High Energy Physics Department:

J. Bartke, E. Gładysz-Dziaduś, E. Górnicki, M. Kowalski, A. Rybicki, P. Stefański and Z. Wlodarczyk<sup>6</sup>).

**Darmstadt, Germany,** Gesellschaft für Schwerionenforschung (GSI): A. Andronic, R. Averbeck, C. Blume, P. Braun-Munzinger, A. Deusser, A. Devismes, J. Eschke, P. Foka, C. Garabatos, B. Kolb, J. Lühning, U. Lynen, A.M. Marin, D. Miśkowiec, W.F.J. Müller, C. Neyer, A. Sandoval, H. Sann, H.R. Schmidt, H. Stelzer and A. Wörner.

**Frankfurt, Germany,** Institut für Kernphysik, Johann-Wolfgang Göthe Universität: C. Bormann, P. Buncic, M. Gaździcki, J. Günther, S. Lange, R. Renfordt, G. Roland, R. Stock and H. Ströbele.

**Gatchina, Russia,** St. Petersburg Nuclear Physics Institute: V. Guersenchtein, B. Komkov, V. Kozlov V. Nikouline, V. Samsonov, O. Tarasenkova, S. Volkov and A. Vorobiev.

**Heidelberg, Germany,** Max-Planck-Institut für Kernphysik: F. Ceretto, C. Fuchs, J. Rak and J.P. Wurm.

**Heidelberg, Germany,** Institut für Hochenergiephysik, Ruprecht-Karls Universität: F.O. Lesser, V. Lindenstruth and A.G.E. Mass.

**Heidelberg, Germany,** Physikalisches Institut, Ruprecht-Karls Universität: H. Appelshäuser, S. Esumi, K. Filimonov, P. Glässel, B. Lenkeit, N. Herrmann, M.J. Richter, W. Schmitz, J. Stachel, H. Tilsner, J.P. Wessels, T. Wienold and B. Windelband.

**Ioannina, Greece,** University of Ioannina, Department of Physics: X. Aslanoglou.

**Jaipur, India,** Physics Department, University of Rajasthan: A. Bharti, S.K. Gupta, R. Raniwala and S. Raniwala.

Jammu, India, Physics Department, Jammu University: S.K. Badyal, A. Bhasin, A. Gupta, V.K. Gupta, L.K. Mangotra, B.V.K.S. Potukuchi, N.K. Rao and S.S. Sambyal.

JINR, Russia, Joint Institute for Nuclear Research:

P.G. Akichine, V.A. Arefiev, V.I. Astakhov, A.A. Baldine, A.M. Baldine, V.D. Bartenev, B.V. Batiounia, I.V. Boguslavsky, Z.V. Borissovskaia, P. Bylinkine, A.V. Chabounov, G.S. Chabratova, I.A. Chichov, V. Danilov, V.I. Datskov, V.K. Dodokhov, L.G. Efimov, A.G. Fedounov, O.A. Golubitsky, B.N. Guouskov, O.I. Iouldachev, V.G. Kadychevsky, I.E. Karpunina, E.K. Koshurnikov, A.D. Kovalenko, A. Lioubimtsev, V.L. Lioubochits, V.I. Lobanov, G.I. Lykasov, E.A. Matiouchevski, K.V. Mikhailov, D.P. Mikhalev, I. Minaev, P.V. Nomokonov, A.N. Parfenov, I.V. Pouzynin, V.N. Pozdnyakov, A.B. Sadovski, A.E. Senner, I.A. Shelaev, A.V. Sidorov, N.V. Slavine, M.K. Suleimanov, G.P. Tsvineva, A.S. Vodopianov, M.B. Yuldasheva, S. Zaporozhets and A.I. Zintchenko.

V. Diomkin<sup>7</sup>), V. Kuznetsov<sup>7</sup>), V. Shestakov<sup>7</sup>), A. Vasiliev<sup>7</sup>) and A. Zhakovksy<sup>7</sup>).

Ts. Baatar<sup>8)</sup>, B. Khurelbaatar<sup>8)</sup> and R. Togoo<sup>8)</sup>.

K.G. Akhobadze<sup>9</sup>, A.K. Djavrishvili<sup>9</sup>, T. Grigalashvili<sup>9</sup>, E.S. Ioramashvili<sup>9</sup>, A.V. Kharadze<sup>9</sup>, L. Khizanishvili<sup>9</sup>, T.V. Khuskivadze<sup>9</sup>, L.V. Shalamberidze<sup>9</sup> and N. Shubitidze<sup>9</sup>.

V. Djordjadze<sup>10)</sup>, N. Grigalashvili<sup>10)</sup>, Z. Menteshashvili<sup>10)</sup>, M. Nioradze<sup>10)</sup>, M. Tabidze<sup>10)</sup> and Y. Tevzadze<sup>10)</sup>.

M. Bondila<sup>11)</sup>, D. Felea<sup>11)</sup>, A. Gheata<sup>11)</sup>, M. Gheata<sup>11)</sup>, M. Haiduc<sup>11)</sup>, D. Hasegan<sup>11)</sup>, R. Marginean<sup>11)</sup>, R.I. Nanciu<sup>11)</sup> and S.I. Zgura<sup>11)</sup>.

**Jyväskylä, Finland,** Department of Physics, University of Jyväskylä and Helsinki Institute of Physics: J. Aysto, V. Ruuskanen and W. Trzaska.

**Kharkov, Ukraine,** National Scientific Centre 'Kharkov Institute of Physics and Technology': G.L. Bochek, V.F. Boldyshev, I.F. Chervonny, A.N. Dovbnya, V.I. Kulibaba, N.I. Maslov, S.M. Potin, I.M. Prokhorets and A.F. Starodubtsev.

**Kharkov, Ukraine,** Scientific and Technological Research Institute of Instrument Engineering: V.N. Borshchov, S.K. Kiprich, O.M. Listratenko, G. Protsay, V.E. Starkov and M. Zamirets.

**Kiev, Ukraine,** Department of High Energy Density Physics, Bogolyubov Institute for Theoretical Physics, National Academy of Sciences of Ukraine: T. Hryn'ova, D.E. Kharzeev, V. Palshin, O. Pavlenko, A. Velytsky and G. Zinovjev.

**Košice, Slovakia,** Institute of Experimental Physics, Slovak Academy of Sciences and Faculty of Science P.J. Šafárik University:

J. Bán, J. Fedorišin, M. Hnatič, A. Jusko, B. Kocper, I. Králik, A. Kravčáková, F. Kriváň, I. Kuľková, M. Lupták, G. Martinská, B. Pastirčák, L. Šándor, J. Urbán, S. Vokál and J. Vrláková.

**Legnaro, Italy,** Laboratori Nazionali di Legnaro: R.A. Ricci.

**Lisbon, Portugal,** Departamento de Física, Instituto Superior Técnico: P. Branco, R. Carvalho, J. Seixas and R. Vilela Mendes.

Lund, Sweden, Division of Cosmic and Subatomic Physics, University of Lund: L. Carlen, S.I.A. Garpman, H.-A. Gustafsson, P. Nilsson, A. Oskarsson, L. Osterman, I. Otterlund, D. Silvermyr and E.A. Stenlund.

**Lyon, France,** Institut de Physique Nucléaire de Lyon (IPNL), IN2P3-CNRS et Université Claude Bernard Lyon-I:

M.Y. Chartoire, M. Chevallier, B. Cheynis, D. Essertaize, E. Galichet, E. Gangler, M. Goyot, J.Y. Grossiord, R. Guernane, A. Guichard, D. Guinet, G. Jacquet, P. Lautesse, M. Miguet and S. Tissot.

**Marburg, Germany,** Fachbereich Physik, Philipps Universität: F. Eckhardt, V. Friese and F. Pühlhofer.

**Mexico City, Mexico,** Centro de Investigación y de Estudios Avanzados (CINVESTAV): R. Hernández Montoya, G. Herrera Corral, L. Magaña-Mendoza, H. Mendez and L.M. Montaño.

**Minsk, Belarus,** Institute for Nuclear Problems, State University: A.A. Lobko.

**Moscow, Russia,** Institute for Nuclear Research, Academy of Science: K.A. Chileev, M.B. Goloubeva, F.F. Gouber, T.L. Karavitcheva, A.B. Kourepin, A.I. Maevskaia, V.I. Razine, A.I. Rechetine, N.S. Topilskaia and N.V. Zaikovskaya.

Moscow, Russia, Institute for Theoretical and Experimental Physics:

A.N. Akindinov, S.V. Boiarinov, V. Golovine, I.G. Grichouk, A.B. Kaidalov, M.M. Kats, I.T. Kiselev, S.M. Kisselev, E. Lioublev, M. Martemianov, A.N. Martemiyanov, P.A. Polozov, S.A. Pozdniakov, V.S. Serov, A.V. Smirnitski, M.M. Tchoumakov, I.A. Vetlitski, K.G. Volochine, L.S. Vorobiev and B.V. Zagreev.

Moscow, Russia, Russian Research Center 'Kurchatov Institute':

V. Antonenko, S. Beliaev, R. Cherbatchev, I. Doubovik, S. Fokine, M. Ippolitov, K. Karadjev, A.L. Lebedev, V. Lebedev, V.I. Manko, G. Mguebrichvili, T. Moukhanova, A. Nianine, S. Nikolaev, S. Nikouline, O. Patarakine, D. Peressounko, I. Sibiriak, A. Vasiliev, A. Vinogradov and M. Volkov.

**Moscow, Russia,** Moscow Engineering Physics Institute: V. Grigoriev, V. Kapline, V. Loguinov and M. Strikhanov.

**Münster, Germany,** Institut für Kernphysik, Westfälische Wilhelms Universität: D. Bucher, T. Peitzmann, K. Reygers, R. Santo, H. Schlagheck and M. Wahn.

Nantes, France, Laboratoire de Physique Subatomique et des Technologies Associées:

L. Aphecetche, T. Bernier, A. Boucham, S. Bouvier, L. Conin, J.P. Cussonneau, H. Delagrange,

D. D'Enterria, B. Erazmus, S. Giliberto, B. Guillet, H.H. Gutbrod, M.S. Labalme, P. Lautridou,

F. Lefèvre, M. Le Guay, L. Luquin, L. Martin, G. Martinez, V. Métivier, M.J. Mora, P. Pichot,

A. Rahmani, O. Ravel, T. Reposeur, F. Retiere, P. Rivoalan, C.S. Roy, D. Roy, Y. Schutz and

A. Tournaire.

**NIKHEF, The Netherlands,** National Institute for Nuclear and High Energy Physics: M. Botje<sup>12)</sup>, A. Buijs<sup>13)</sup>, J.J.F. Buskop<sup>12)</sup>, A.P. De Haas<sup>13)</sup>, P.K.A. De Witt Huberts<sup>12,13)</sup>, R. Kamermans<sup>12,13)</sup>, P.G. Kuijer<sup>12,13)</sup>, D. Muigg<sup>13)</sup>, G. Nooren<sup>12)</sup>, C.J. Oskamp<sup>13)</sup>, A. Van Den Brink<sup>13)</sup>, N. Van Eijndhoven<sup>13)</sup> and J. Visschers<sup>12)</sup>.

**Novosibirsk, Russia,** Budker Institute for Nuclear Physics: A.R. Frolov, I.N. Pestov and M.A. Tiounov.

**Oak Ridge, U.S.A.,** Instrumentation and Controls Division, Oak Ridge National Laboratory: C.L. Britton, W.L. Bryan, J.W. Walker and A.L. Wintenberg.

**Orsay, France,** Institut de Physique Nucléaire, Université de Paris-Sud: L. Bimbot, P.F. Courtat, R. Douet, P. Edelbruck, B. Genolini, H. Harroch, D. Jouan, L. Kharmandarian, Y. Le Bornec, M. Mac Cormick, J. Peyré, J. Pouthas, R. Sellem and N. Willis.

**Oslo, Norway,** Department of Physics, University of Oslo: A.K. Holme, L.M. Ingebrigtsen, G. Løvhøiden, B. Skaali, T.S. Tveter and D. Wormald.

**Padua, Italy,** Dipartimento di Fisica dell'Università and Sezione INFN: F. Antinori, F. Brandolini, N. Carrer, M. Morando, A. Pepato, F. Scarlassara, G. Segato, F. Soramel and E. Zanoni.

**Prague, Czech Republic,** Institute of Physics, Academy of Science: J. Mareš, E. Mihoková, M. Nikl, K. Píška, K. Polák and P. Závada.

Protvino, Russia, Institute for High Energy Physics:

A.M. Blik, M. Bogolyubsky, G. Britvitch, S. Erine, G.V. Khaoustov, I.V. Kharlov, V.N. Kolossov, V. Lichine, M. Lobanov, S.A. Sadovski, V.D. Samoilenko, P.A. Semenov, V.I. Suzdalev, V. Tikhonov and A. Zviagine.

**Řež u Prahy, Czech Republic,** Academy of Sciences of Czech Republic, Nuclear Physics Institute: V. Hanzal, J. Hošek, I. Hřivnáčová, V. Kuschpil, A. Kugler, V. Petráček, M. Šumbera, A. Tlustý, V. Wagner and D. Zákoucký.

**Rome, Italy,** Dipartimento di Fisica dell'Università 'La Sapienza' and Sezione INFN: S. Di Liberto, M.A. Mazzoni, F. Meddi, D. Prosperi and G. Rosa.

Saclay, France, Centre d'Etudes Nucléaires, DAPNIA/SPhN: P. Ageron, A. Baldisseri, H. Borel, I. Chevrot, P. De Girolamo, J. Gosset, L. Gosset, P. Hardy, J.C. Lugol, F.M. Staley and Y. Terrien.

Salerno, Italy, Università di Salerno and Sezione INFN: L. Cifarelli, B. Cozzoni, A. De Caro, G. Grella, M. Guida, A. Lavorato, J. Quartieri, G. Romano, A. Seganti, D. Vivinanza and T. Virgili.

Sarov, Russia, Russian Federal Nuclear Center (VNIIEF):

S. Abramovitch, V. Basmanov, V. Ianowski, R. Ilkaev, L. Ilkaeva, A. Ivanov, A. Khlebnikov,

E. Kolokolnikov, V. Matiev, S. Nazarenko, V. Pounine, S. Poutevskoi, I. Selin, M. Tarasov,

I. Vinogradov, S. Zhelezov and A. Zhitnik.

**St. Petersburg, Russia,** Institute for Physics of St. Petersburg State University, Mendeleev Institute for Metrology and Meson Scientific Association:

L.Y. Abramova, V.S. Alexandrov, V.M. Baratov, A.A. Bolonine, M.A. Braun, V.M. Dobulevitch,G.A. Feofilov, O.N. Godissov, S. Guerassimov, S.N. Igolkine, M.I. Ioudkine, A.A. Kolojvari,V. Kondratiev, I.A. Novikov, S.V. Potapov, O.I. Stolyarov, T.A. Toulina, F.A. Tsimbal, F.F. Valiev,V.V. Vetchernine, L.I. Vinogradov and L.F. Vitouchkine.

Strasbourg, France, Institut de Recherches Subatomiques:

L. Arnold, M. Ayachi, J. Baudot, J.D. Berst, J.P. Blondé, D. Bonnet, J.P. Coffin, W. Dulinski, M. Germain, G. Guillaume, L. Hebrard, Y. Hu, F. Jundt, C. Kuhn, J. Lutz, A. Michalon, F. Rami, C. Suire and A. Tarchini.

**Trieste, Italy,** Dipartimento di Fisica dell'Università and Sezione INFN: V. Bonvicini, L. Bosisio, P. Camerini, A. Gregorio, N. Grion, G. Margagliotti, C. Piemonte, A. Rachevski, R. Rui, A. Vacchi and N. Zampa.

Turin, Italy, Dipartimenti di Fisica dell'Università and INFN:

G. Alberici, B. Alessandro, R. Arnaldi, S. Beolé, G. Bonazzola, L. Busso, D. Cavagnino, P. Cerello,

E. Chiavassa, P. Cortese, E. Crescio, F. Daudo, N. De Marco, P. De Remigis, A. Feliciello, M. Gallio,

G. Giraudo, P. Giubellino, A. Marzari-Chiesa, M. Masera, G. Mazza, P. Mereu, B. Minetti, A. Musso,

D. Nouais, A. Piccotti, G. Piragino, L. Riccati, E. Scomparin, L. Simonetti, F. Tosello, E. Vercellin,

A. Werbrouck and R. Wheadon.

Warsaw, Poland, Soltan Institute for Nuclear Studies:

D. Czerwinski, A. Deloff, K. Karpio, S. Kozak, L. Lukaszek, H. Malinowski, T. Siemiarczuk, G. Stefanek, L. Tykarski and G. Wilk.

Warsaw, Poland, University of Technology, Institute of Physics: J. Grabski, M. Janik, P. Kindziuk, A. Kisiel, P. Leszczynski, A.M. Maliszewski, J.M. Mazur, T.J. Pawlak, P. Pery, W.S. Peryt, J. Pluta, M. Przewlocki, S. Radomski, A.M. Roszczewski, P. Skowronski, P. Stepien and P. Szarwas.

**Wuhan, China,** Institute of Particle Physics, Huazhong Normal University: X. Cai, Y. Hu, F. Liu, L. Liu, H. Wang and D. Zhou.

#### Yerevan, Armenia, Yerevan Physics Institute:

R. Asatryan, M. Atayan, R. Avakian, V. Danielyan, V. Gavalian, A. Grigorian, S. Grigoryan, H. Gulkanyan, R. Hakobyan, V. Kakoyan, S. Mehrabyan, L. Parlakyan, R. Shahoyan and H. Vardanyan.

**Zagreb, Croatia,** Ruder Bošković Institute: D. Ferenc, A. Ljubičić and T. Tustonic.

<sup>&</sup>lt;sup>1)</sup> Also at CERN, Geneva, Switzerland

<sup>&</sup>lt;sup>2)</sup> On leave from JINR, Dubna, Russia.

<sup>&</sup>lt;sup>3)</sup> On leave from IHEP, Protvino, Russia.

<sup>&</sup>lt;sup>4)</sup> On leave from Budapest University, Hungary.

<sup>&</sup>lt;sup>5)</sup> On leave from Dipartimento di Fisica dell'Universitá and Sezione INFN, Padua, Italy.

<sup>&</sup>lt;sup>6)</sup> Institute of Physics, Pedagogical University, Kielce, Poland.

<sup>&</sup>lt;sup>7)</sup> Research Centre for Applied Nuclear Physics (RCANP), Dubna, Russia.

<sup>&</sup>lt;sup>8)</sup> Institute of Physics and Technology, Mongolian Academy of Sciences, Ulaanbaatar, Mongolia.

<sup>&</sup>lt;sup>9)</sup> Institute of Physics, Georgian Academy of Sciences, Tbilisi, Georgia.

<sup>&</sup>lt;sup>10)</sup> High Energy Physics Institute, Tbilisi State University, Tbilisi, Georgia.

<sup>&</sup>lt;sup>11)</sup> Institute of Space Sciences, Bucharest, Romania.

<sup>&</sup>lt;sup>12)</sup> Foundation of Fundamental Research of Matter in The Netherlands.

<sup>&</sup>lt;sup>13)</sup> Utrecht University, Utrecht, The Netherlands.

### Acknowledgements

It is a pleasure to acknowledge the contribution given to the preparation of this TDR by: G. Alfarone, Y. Ansel, D. Balke, M. Bosteels, N. Bouillo, L. Caponetto, H. Carduner, M. Caselle, A. Chlopik, C. D'Ambrosio, M. Dialinas, C. Gojak, G. Guilloux, P. van Haren, L.A. Kiprich, R. Kluit, C. LeMoal, P. Lisco, D. Maniero, S. Martini, D. Mazzaro, N.M. Mikhailova, J. Nissinen, H.Z. Peek, W. Pinganaud, A.P. Reznik, F. Rotondo, L.N. Ruzhitskaya, V.M. Ruzhitsky, M. Turcato, L.I. Tverdokhleb and K. Wyllie.

The editorial board, L. Riccati, F. Antinori, J.P. Coffin, P .Giubellino, P.G. Kuijer, K. Šafařík, F. Tosello and A. Vacchi, wishes to thank all the technical and administrative staff (in particular S. Barras and S. Stappers) involved during the preparation of this TDR. We also thank the Desktop Publishing Service, for their professional help with the editing.

| 1 Intro | oduction                                                        | 1  |

|---------|-----------------------------------------------------------------|----|

| 1.1     | The ALICE experiment                                            | 1  |

| 1.2     | General considerations                                          | 1  |

| 1.2.1   | Tracking in ALICE                                               | 1  |

| 1.2.2   | Physics of the ITS                                              | 2  |

| 1.2.3   | Design considerations                                           | 3  |

| 1.2.4   | Layout of the ITS                                               | 4  |

| 1.3     | Design of the pixel layers                                      | 6  |

| 1.3.1   | Detector overview                                               | 7  |

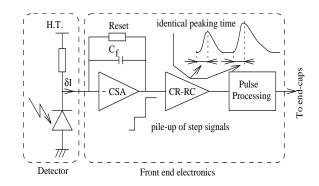

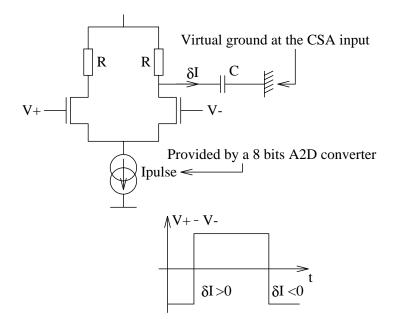

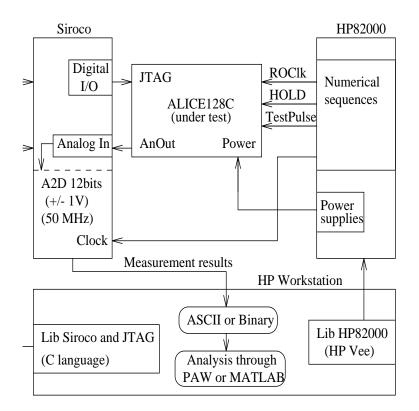

| 1.3.2   | Front-end electronics                                           | 7  |

| 1.3.3   | Readout and control                                             | 8  |

| 1.4     | Design of the drift layers                                      | 8  |

| 1.4.1   | The SDDs                                                        | 9  |

| 1.4.2   | The SDD readout                                                 | 9  |

| 1.4.3   | The SDD ladders                                                 | 10 |

| 1.5     | Design of the strip layers                                      | 10 |

| 1.5.1   | The SSD module                                                  | 11 |

| 1.5.2   | The SSDs                                                        | 11 |

| 1.5.3   | The SSD electronics                                             | 12 |

| 1.5.4   | The SSD cooling system                                          | 12 |

| 1.6     | Performance of the ITS                                          | 13 |

| 1.6.1   | Tracking consideration                                          | 13 |

| 1.6.2   | Material budget                                                 | 13 |

| 1.6.3   | Track reconstruction                                            | 14 |

| 1.6.4   | Particle identification                                         | 15 |

| 1.6.5   | Particle correlations                                           | 15 |

| 1.6.6   | Hyperon detection                                               | 15 |

| 1.6.7   | Detection of open charm                                         | 16 |

|         |                                                                 |    |

|         | Silicon Pixel Layers                                            | 17 |

|         | Front-end chip                                                  | 17 |

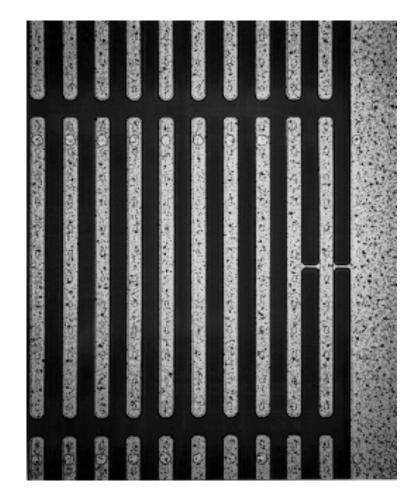

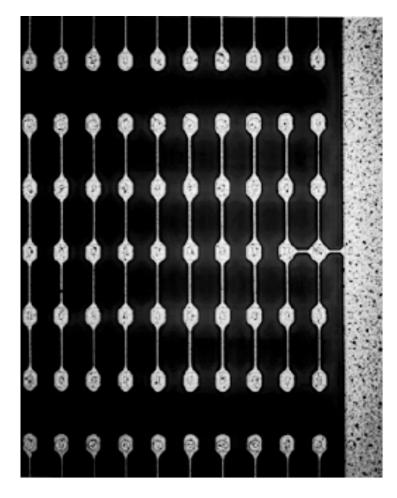

| 2.1.1   | The Omega2 front-end chip                                       | 17 |

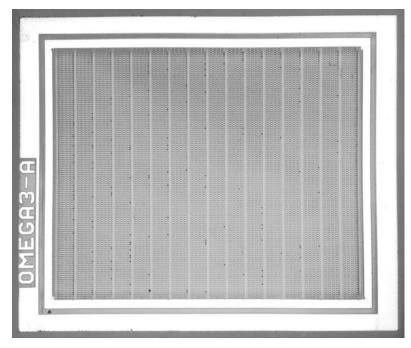

| 2.1.2   | The Omega3 front-end chip                                       | 20 |

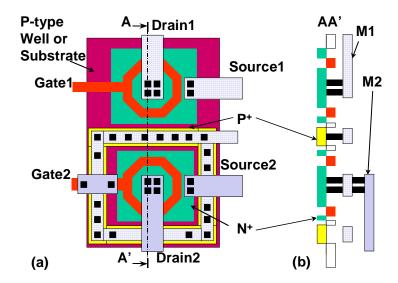

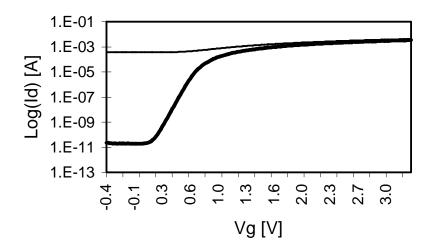

| 2.1.3   | Gate-all-around CMOS design                                     | 22 |

| 2.1.4   | The Alice1Test chip                                             | 26 |

| 2.1.5   | The Alice2Test chip                                             | 32 |

| 2.1.6   | The Alice1 front-end chip                                       | 38 |

|         | Detector modules                                                | 41 |

| 2.2.1   | Omega2 and Omega3 detector ladders                              | 41 |

| 2.2.2   | ALICE detector ladders                                          | 45 |

| 2.2.3   | Flip-chip assembly                                              | 45 |

| 2.2.4   | Component qualification                                         | 47 |

|         | Bussing, readout and control                                    | 48 |

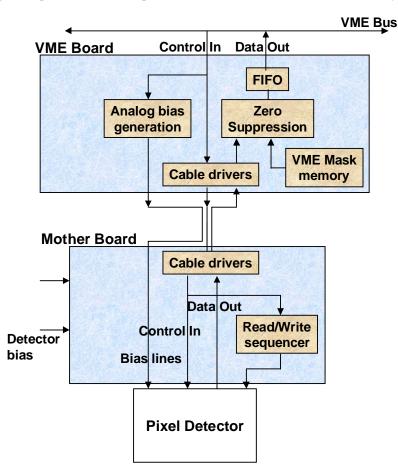

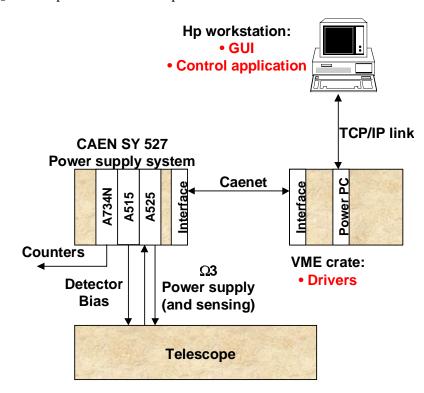

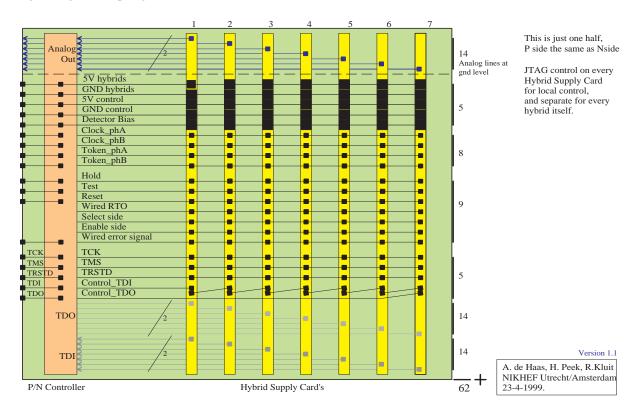

| 2.3.1   | Bussing, readout, and control for the Omega2 and Omega3 systems | 48 |

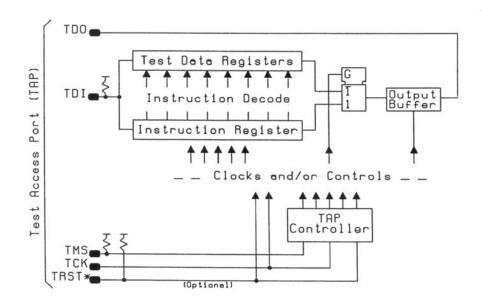

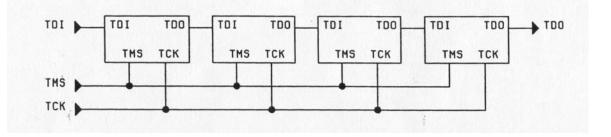

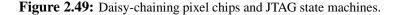

| 2.3.2   | JTAG control                                                    | 52 |

| 2.3.3   | Readout logic                                                   | 59 |

| 2.3.4          | Stave bus                         | 63  |

|----------------|-----------------------------------|-----|

| 2.3.5          | Short data link                   | 64  |

| 2.4            | Assembly, mechanics and cooling   | 67  |

| 2.4.1          | Introduction                      | 67  |

| 2.4.2          | Stave assembly                    | 68  |

| 2.4.3          | Carbon-Fibre Support Sector       | 69  |

| 2.4.4          | CFSS prototyping                  | 72  |

| 2.4.5          | Sector assembly                   | 75  |

| 2.4.6          | Cooling system                    | 75  |

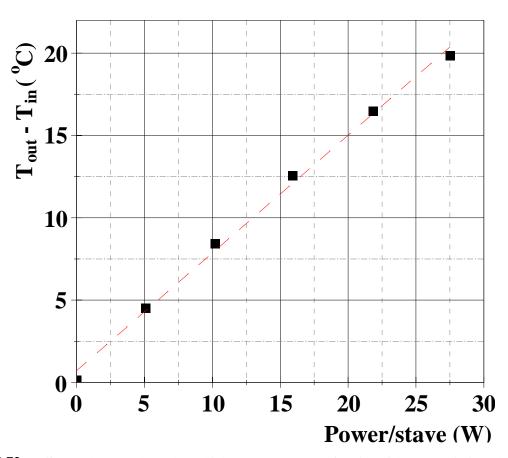

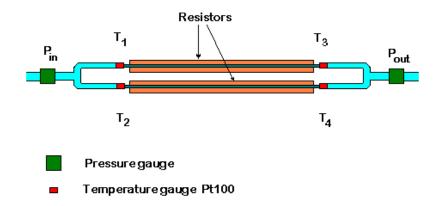

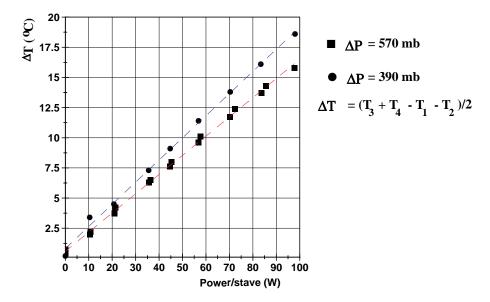

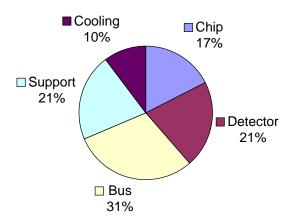

| 2.4.7          | Cooling tests                     | 77  |

| 2.4.8          | -                                 | 79  |

| 2.4.9          |                                   | 79  |

| 2.5            |                                   | 81  |

|                |                                   |     |

| 3 The          | Silicon Drift Layers              | 83  |

| 3.1            | The ALICE Silicon Drift Detectors | 85  |

| 3.1.1          | Introduction                      | 85  |

| 3.1.2          | The Silicon Drift Detectors       | 86  |

| 3.1.3          | Basic SDD                         | 87  |

| 3.1.4          | The material                      | 88  |

| 3.1.5          |                                   | 88  |

| 3.1.6          |                                   | 89  |

| 3.1.7          |                                   | 92  |

| 3.1.8          |                                   | 93  |

| 3.1.9          | 8                                 | 96  |

| 3.2            |                                   | 96  |

| 3.2.1          |                                   | 96  |

| 3.2.2          |                                   | 98  |

| 3.2.3          |                                   |     |

| 3.2.4          |                                   |     |

| 3.2.5          |                                   |     |

| 3.3            | Drift electronics                 |     |

| 3.3.1          |                                   |     |

| 3.3.2          |                                   |     |

| 3.3.3          | 1                                 |     |

| 3.3.4          | 5                                 |     |

| 3.3.5          | e                                 |     |

| 3.3.6          | 1 51                              |     |

| 3.3.7          |                                   |     |

| 3.3.8          | 8                                 |     |

| 3.4            | Power consumption and cabling     |     |

| 3.4.1          | The low-voltage power consumption |     |

| 3.4.2          |                                   |     |

| 3.5            | The ladder structure              |     |

| 3.5.1          |                                   |     |

| 3.5.1<br>3.5.2 | Overview                          |     |

| 3.5.2<br>3.5.3 | 11                                |     |

|                |                                   |     |

| 3.5.4          | 5                                 |     |

| 3.5.5          | 6                                 |     |

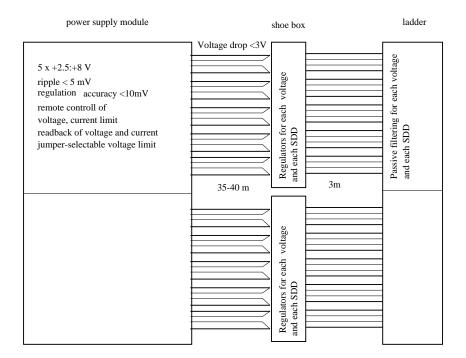

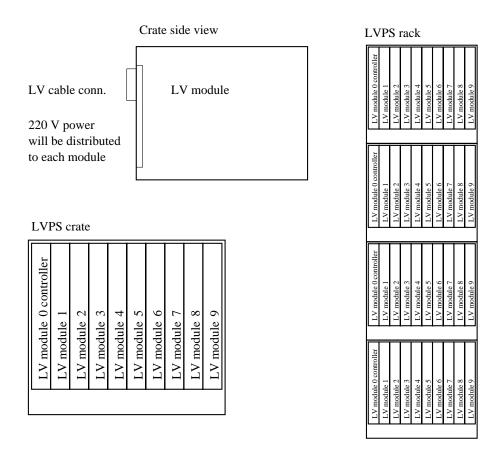

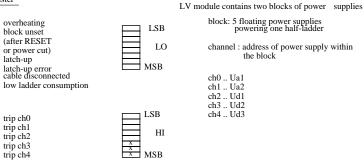

| 3.6            | Power supplies                    | 101 |

| 3.6.1  | The low-voltage power supply system                 |

|--------|-----------------------------------------------------|

| 3.6.2  | The high-voltage power supply system                |

| 3.7    | The SDD simulation                                  |

| 3.7.1  | Program structure                                   |

| 3.7.2  | Results                                             |

| 4 (17) |                                                     |

|        | Silicon Strip Layers 175                            |

|        | Double-Sided Silicon Strip Detectors                |

| 4.1.1  | General detector overview                           |

| 4.1.2  | Prototype quality tests                             |

| 4.1.3  | Detector prototype performance in beam tests        |

| 4.1.4  | Production tests                                    |

| 4.1.5  | Resolution at normal incidence                      |

| 4.1.6  | Optimization of the cluster position reconstruction |

| 4.1.7  | Resolution as a function of the incident angle      |

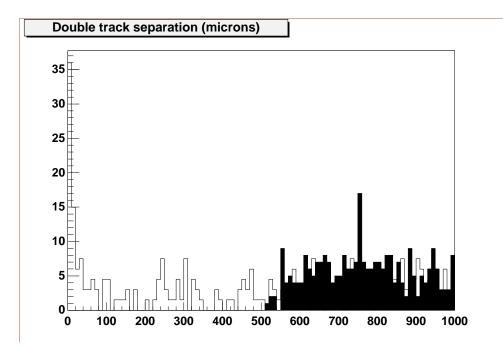

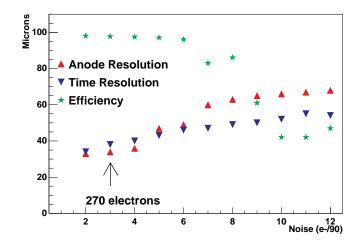

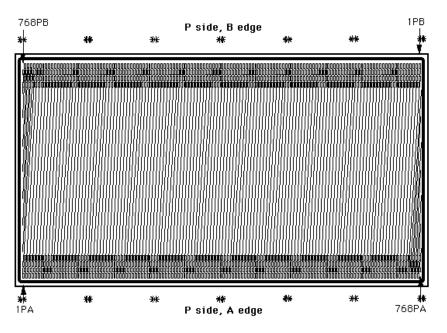

| 4.1.8  | Two-track resolution                                |

| 4.1.9  | Simulation of the silicon strip detector            |

| 4.1.10 |                                                     |

| 4.1.1  | I                                                   |

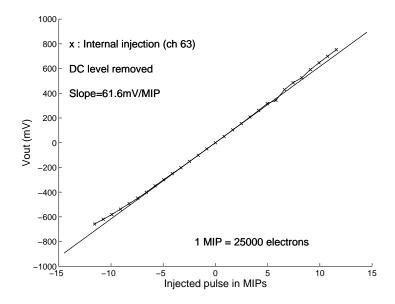

|        | A128C Front-end Chip                                |

| 4.2.1  | Introduction                                        |

| 4.2.2  | Chip tests                                          |

| 4.2.3  | Chip characteristics                                |

| 4.2.4  | A128C production tests                              |

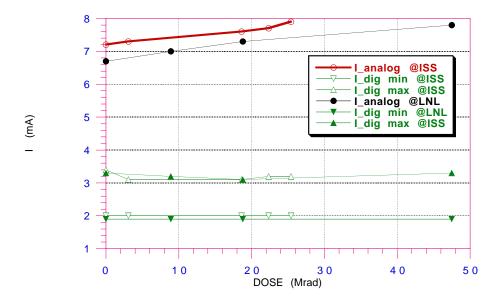

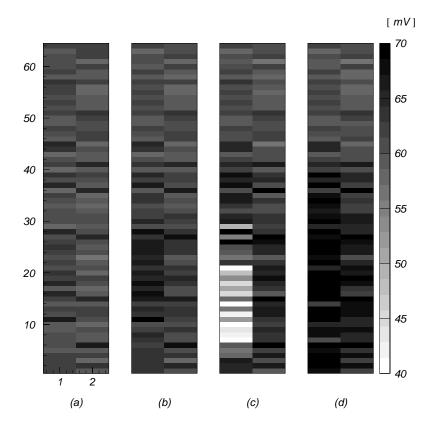

|        | Front-end component irradiation tests               |

| 4.3.1  | SSD-structure results                               |

| 4.3.2  | A128C chip results                                  |

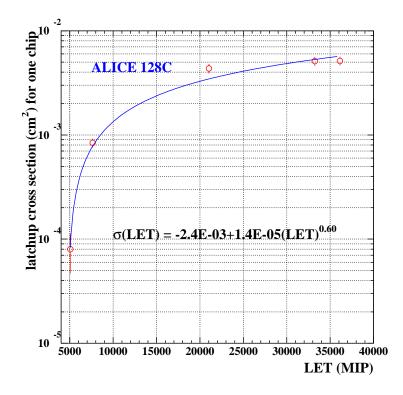

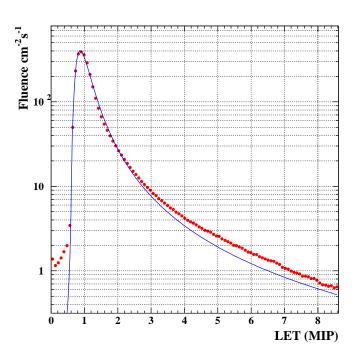

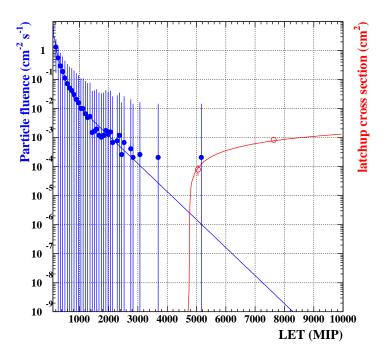

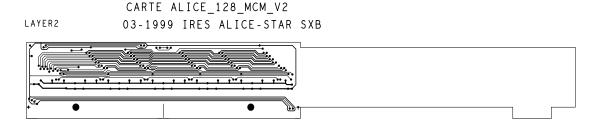

| 4.3.3  | Latch-up sensitivity                                |

|        | Front-end module                                    |

| 4.4.1  | Single-sided hybrids                                |

| 4.4.2  | Double-sided hybrids                                |

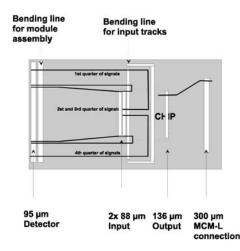

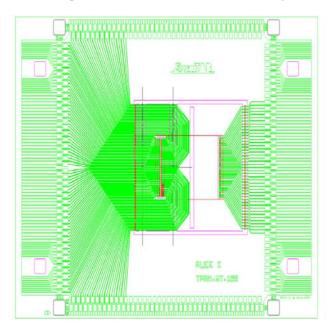

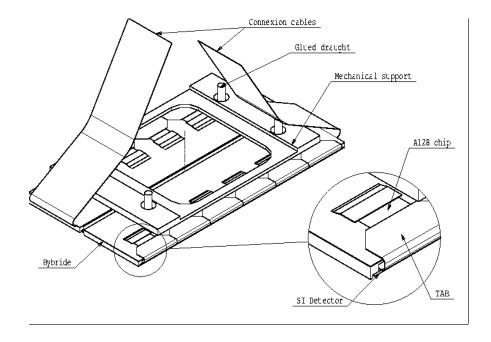

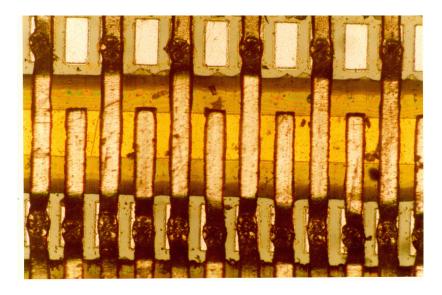

|        | Microcables and TAB bonding                         |

| 4.5.1  | Introduction                                        |

| 4.5.2  | Prototypes                                          |

| 4.5.3  | Large-scale testing and bonding                     |

|        | Readout system                                      |

| 4.6.1  | General description                                 |

| 4.6.2  | Reliability aspects                                 |

| 4.6.3  | End-cap module                                      |

| 4.6.4  | Interconnections                                    |

| 4.6.5  | The front-end readout modules                       |

|        | Detector control and slow control                   |

| 4.7.1  | Slow control                                        |

| 4.7.2  | Detector control                                    |

| 4.7.3  | Physical implementation of control                  |

|        | Mechanical support structure                        |

| 4.8.1  | Position accuracy and stability                     |

| 4.8.2  | Ladder design with wound fibres                     |

| 4.8.3  | Moulded fibre ladder design                         |

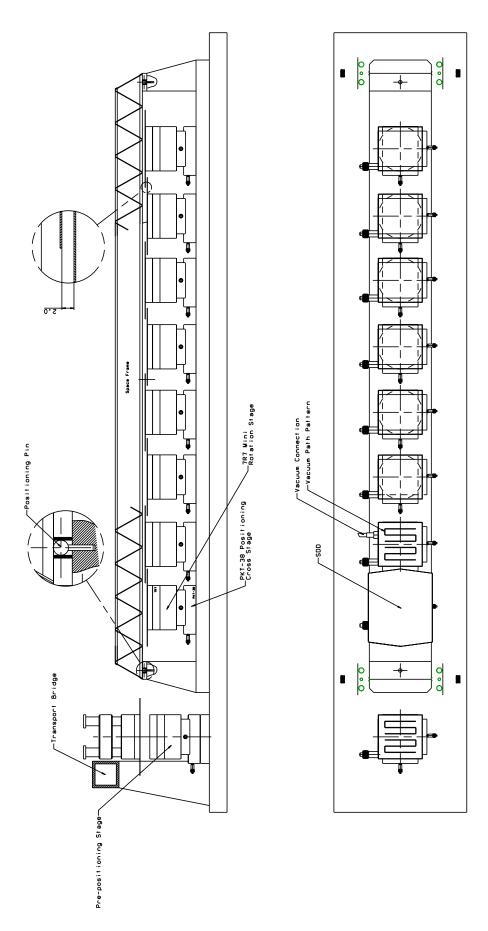

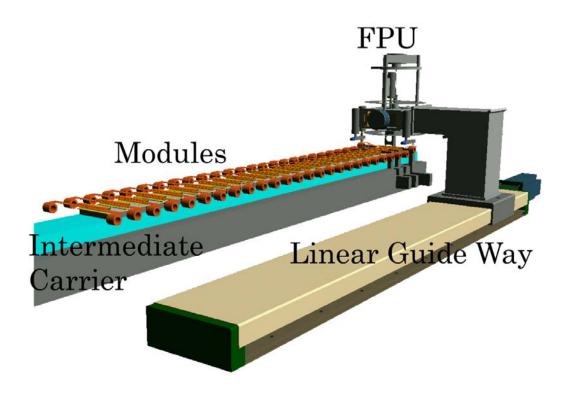

| 4.9    | Ladder Assembly                                     |

| 4.9.1  | Requirements                                                                                                                          | 2     |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.9.2  | Proposed solution                                                                                                                     | 2     |

| 4.9.3  | Assembly scenario                                                                                                                     | 3     |

| 4.9.4  | Assembly machine                                                                                                                      |       |

| 4.10   | Cooling system                                                                                                                        |       |

| 4.10.1 |                                                                                                                                       |       |

| 4.10.2 |                                                                                                                                       |       |

| 4.10.3 |                                                                                                                                       |       |

| 4.11   | Infrastructure                                                                                                                        |       |

| 4.11.1 |                                                                                                                                       |       |

| 4.11.2 |                                                                                                                                       |       |

| 4.11.3 |                                                                                                                                       |       |

| 4.11.4 |                                                                                                                                       |       |

|        |                                                                                                                                       | ,<br> |

| 5 ITS  | Physics Performance 26                                                                                                                | 5     |

|        | Simulations                                                                                                                           | 5     |

| 5.1.1  | ITS description in simulations                                                                                                        | 5     |

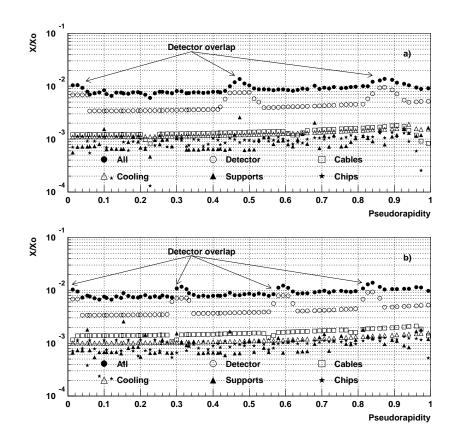

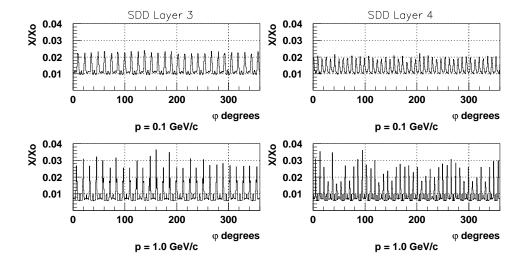

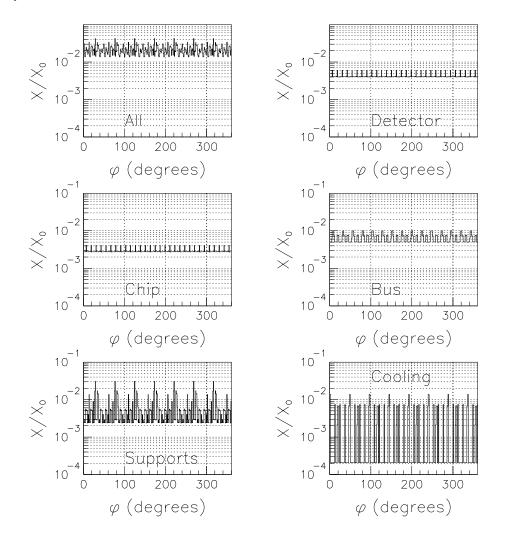

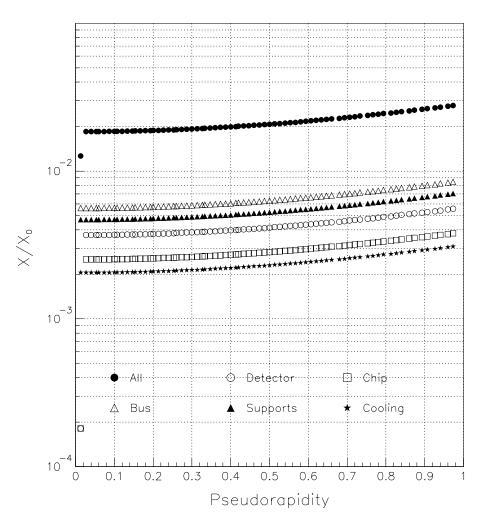

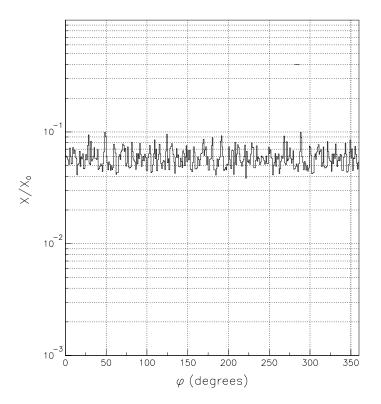

| 5.1.2  | Material budget                                                                                                                       |       |

| 5.1.3  | Particle densities                                                                                                                    |       |

|        | Reconstruction performance                                                                                                            |       |

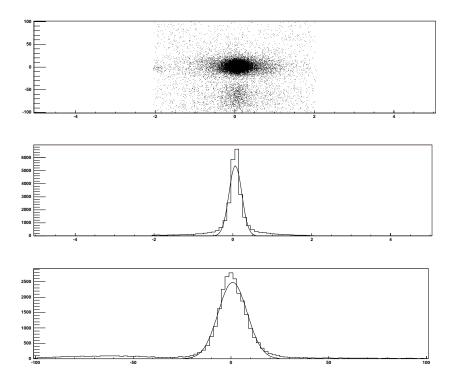

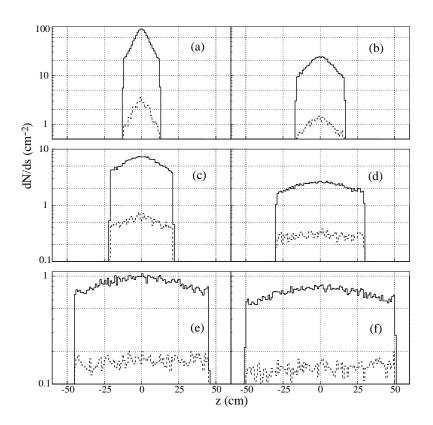

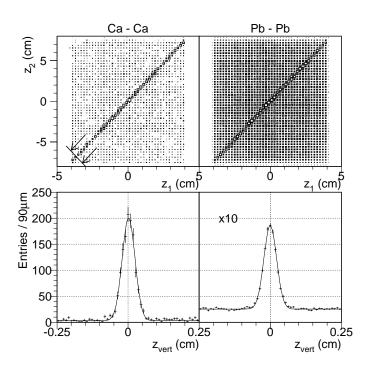

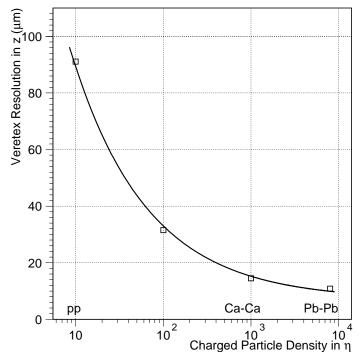

| 5.2.1  | Vertex reconstruction with SPD layers                                                                                                 |       |

| 5.2.2  | Track reconstruction                                                                                                                  |       |

| 5.2.2  | Stand-alone tracking with ITS                                                                                                         |       |

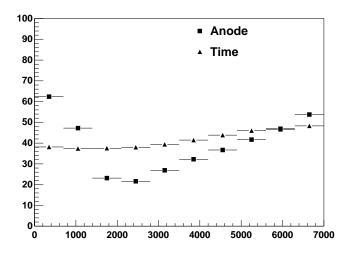

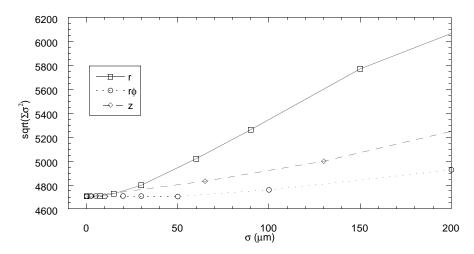

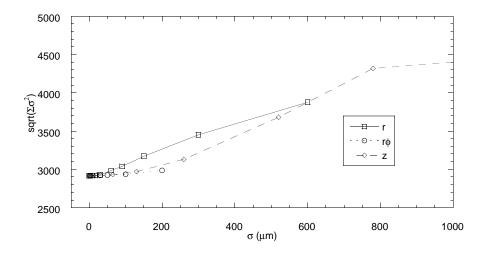

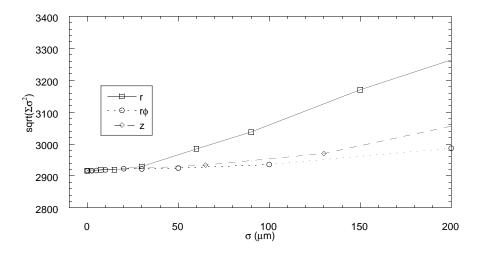

| 5.2.4  | Track parameter resolutions                                                                                                           |       |

|        | Particle identification                                                                                                               |       |

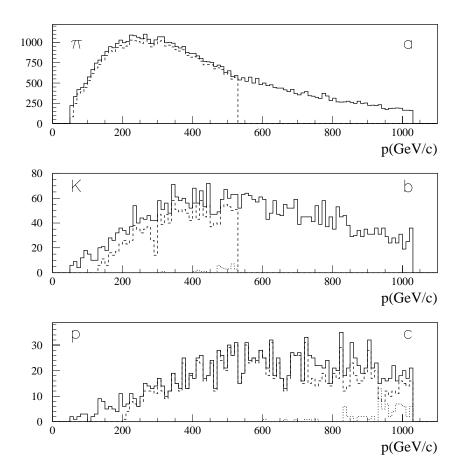

| 5.3.1  | dE/dx measurement                                                                                                                     |       |

| 5.3.2  | Electron/pion separation                                                                                                              |       |

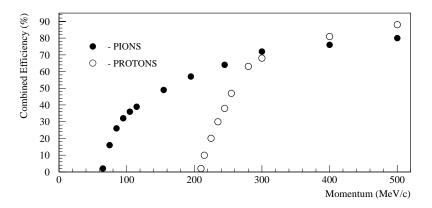

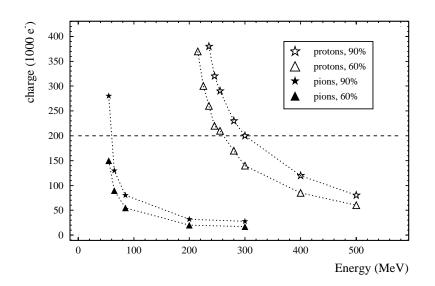

| 5.3.2  | Hadron identification                                                                                                                 |       |

|        |                                                                                                                                       |       |

|        | Particle correlations                                                                                                                 |       |

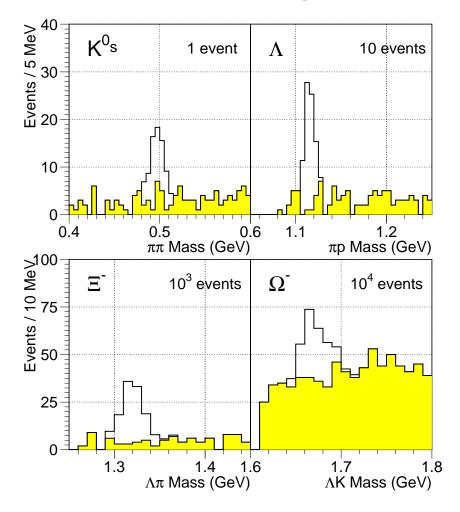

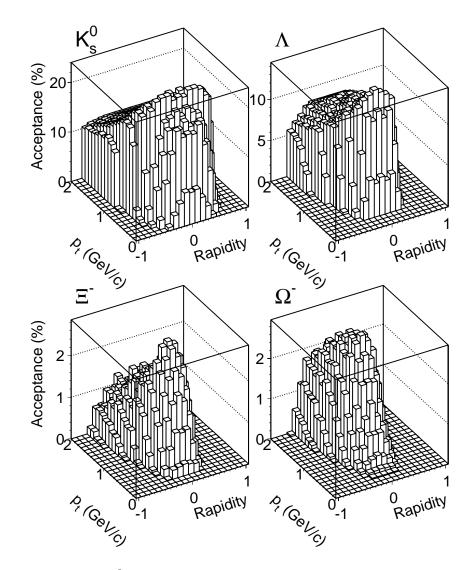

|        | Hyperon detection $\dots \dots \dots$ |       |

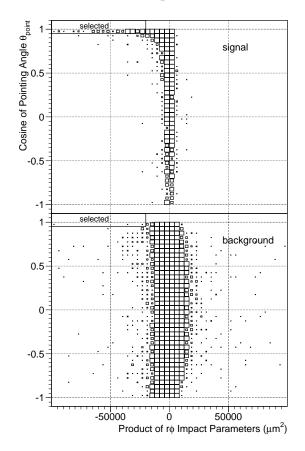

| 5.5.1  | Detection of $V^0$ decays and cascades                                                                                                |       |

| 5.5.2  | Expected hyperon yields                                                                                                               |       |

|        | Open charm detection                                                                                                                  |       |

| 5.6.1  | Experimental approach                                                                                                                 |       |

| 5.6.2  | Simulation for charm                                                                                                                  |       |

| 5.6.3  | D meson detection                                                                                                                     |       |

|        | ITS radiation dose                                                                                                                    |       |

| 5.7.1  | Detector simulation                                                                                                                   |       |

| 5.7.2  | Results of the simulation                                                                                                             | l     |

| ( ()   | 20                                                                                                                                    | -     |

|        | eral mechanics and assembly, alignment, DAQ, slow control, and integration 30 <sup>o</sup>                                            |       |

|        | ITS general support structure                                                                                                         |       |

| 6.1.1  | Design considerations                                                                                                                 |       |

| 6.1.2  | The support structure                                                                                                                 |       |

| 6.1.3  | ITS assembly procedure                                                                                                                |       |

|        | ITS alignment system                                                                                                                  |       |

| 6.2.1  | Possible sources of deformation of the ITS                                                                                            |       |

| 6.2.2  | Monitoring possible deformations and torsion of the ITS support structure                                                             |       |

|        | Alignment system (software)                                                                                                           |       |

| 6.3.1  | Global misalignments                                                                                                                  | 3     |

| 6.3.2 | Local misalignments                                    | 319 |

|-------|--------------------------------------------------------|-----|

| 6.3.3 | Experience of other experiments                        | 319 |

| 6.3.4 | Measurements of misalignment                           | 321 |

| 6.3.5 | Realignment techniques                                 | 321 |

| 6.3.6 | Conclusion                                             | 327 |

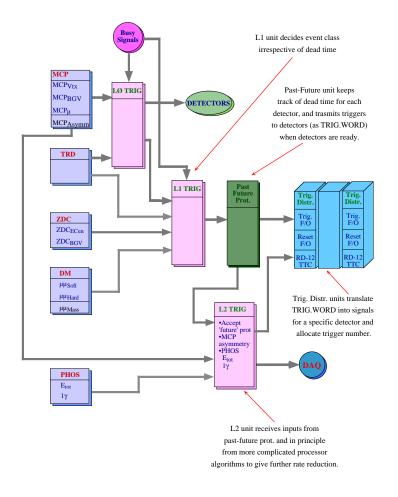

| 6.4   | Trigger and data acquisition system                    | 327 |

| 6.4.1 | Trigger and data acquisition requirements              | 327 |

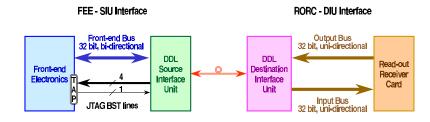

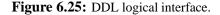

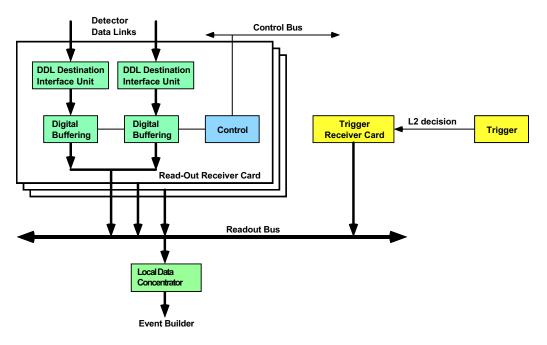

| 6.4.2 | Data transfer components                               |     |

| 6.4.3 | Pixel detector data transfer                           | 331 |

| 6.4.4 | Drift detector data transfer                           | 332 |

| 6.4.5 | Strip detector data transfer                           | 332 |

| 6.4.6 | Data acquisition software                              | 333 |

| 6.5   | Slow controls                                          | 333 |

| 6.5.1 | General and ITS-specific slow control architecture     | 333 |

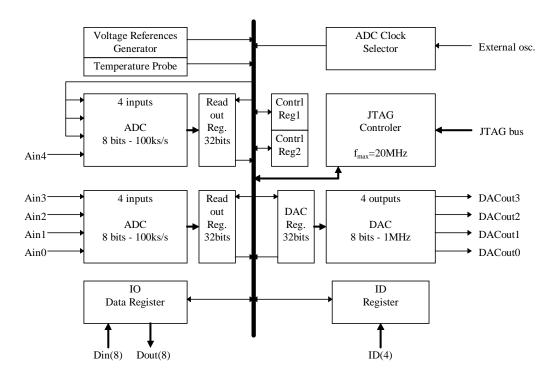

| 6.5.2 | Hardware                                               | 334 |

| 6.5.3 | Communication                                          | 337 |

| 6.5.4 | Software                                               | 337 |

| 6.6   | Safety                                                 | 338 |

| 6.7   | Integration and installation                           | 338 |

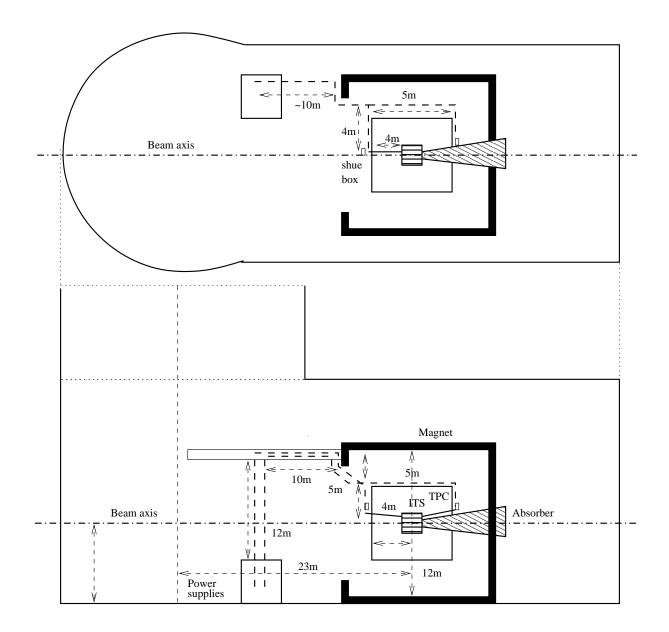

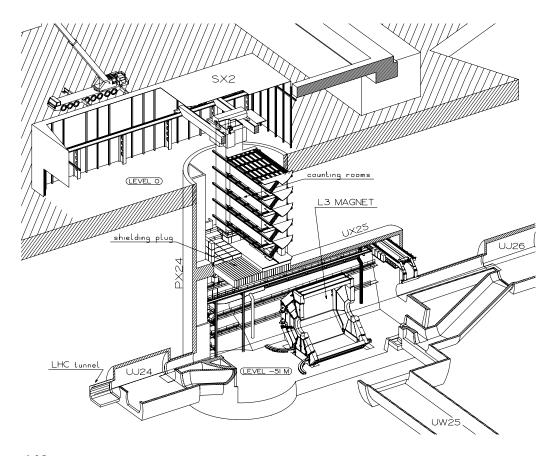

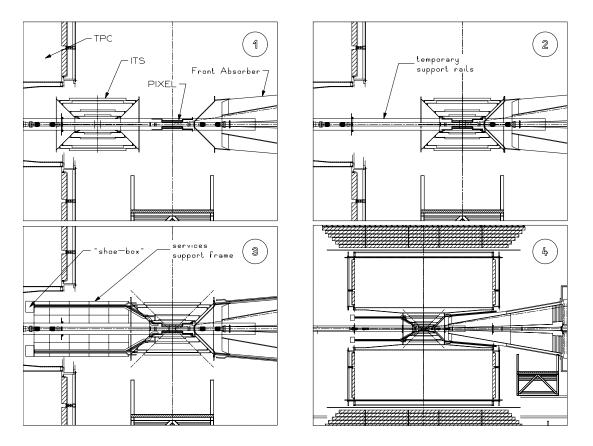

| 6.7.1 | ALICE experimental area                                | 338 |

| 6.7.2 | Installation of the ITS detector                       | 338 |

| 6.7.3 | Services                                               | 343 |

| 6.7.4 | Cables                                                 | 345 |

| 6.7.5 | Power supply location                                  | 345 |

| 7 Org | anization and Planning                                 | 347 |

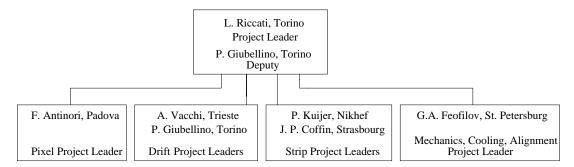

| 7.1   | Organization                                           | 347 |

| 7.1.1 | The ITS working group and the participating institutes |     |

| 7.1.2 | Sharing of responsibilities                            |     |

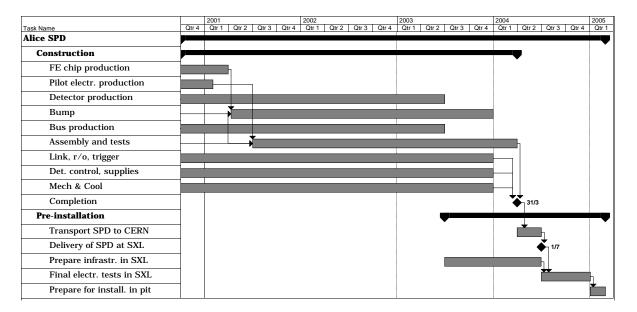

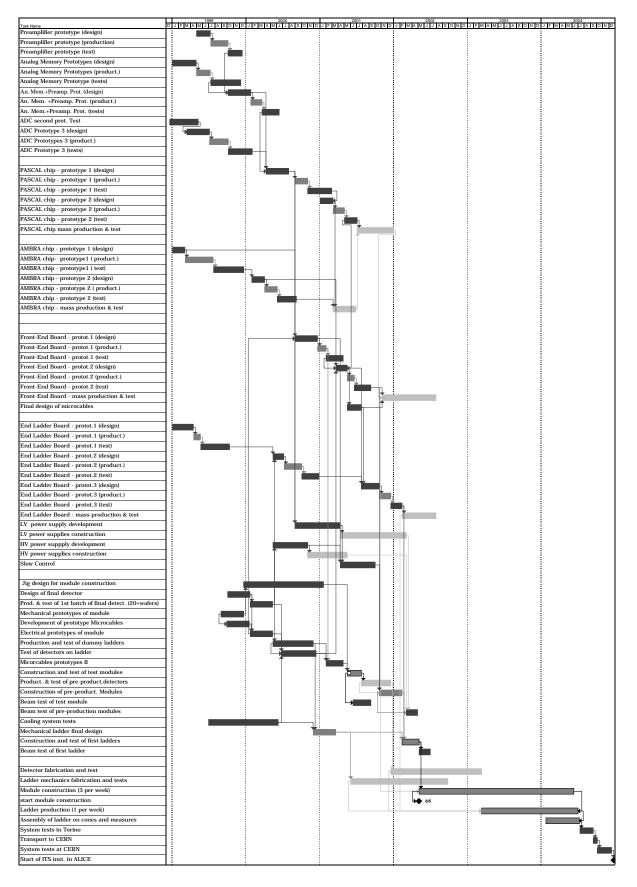

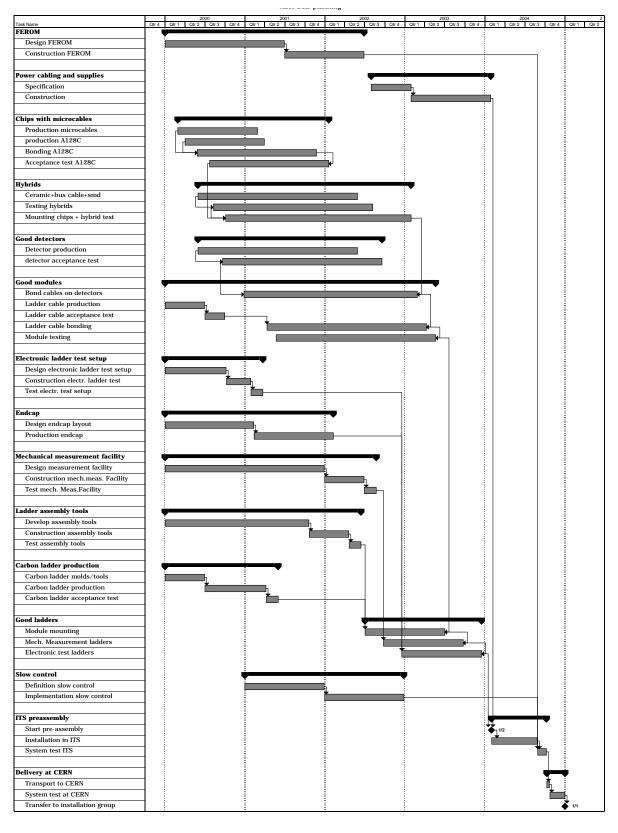

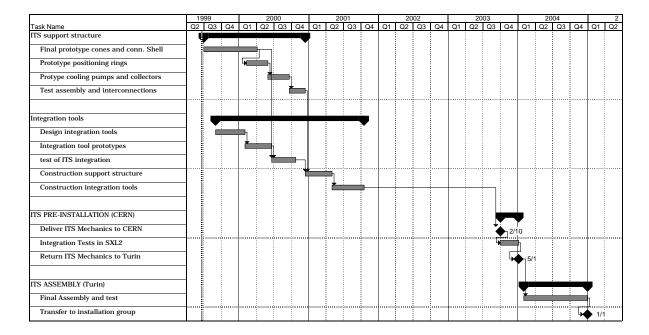

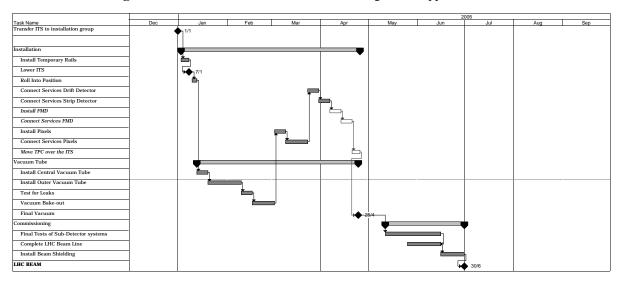

| 7.2   | Planning and construction milestones                   |     |

| 7.3   | Cost estimate and resources                            |     |

|       |                                                        |     |

# References

355

xiv

# **1.1 The ALICE experiment**

ALICE (A Large Ion Collider Experiment) [1] is an experiment at the Large Hadron Collider (LHC) optimized for the study of heavy-ion collisions, at a centre-of-mass energy  $\sim 5.5$  TeV per nucleon. The prime aim of the experiment is to study in detail the behaviour of nuclear matter at high densities and temperatures, in view of probing deconfinement and chiral symmetry restoration.

The detector consists essentially of two main components: the central part, composed of detectors mainly devoted to the study of hadronic signals and dielectrons, and the forward muon spectrometer, devoted to the study of quarkonia behaviour in dense matter. The layout of the ALICE set-up is shown in Colour Fig. I. A major technical challenge is imposed by the large number of particles created in the collisions of lead ions. There is a considerable spread in the currently available predictions for the multiplicity of charged particles produced in a central Pb–Pb collision. The design of the experiment has been based on the highest value, 8000 charged particles per unit of rapidity, at midrapidity. This multiplicity dictates the granularity of the detectors and their optimal distance from the colliding beams.

The central part, which covers  $\pm 45^{\circ}$  ( $|\eta| < 0.9$ ) over the full azimuth, is embedded in a large magnet with a weak solenoidal field. Outside of the Inner Tracking System (ITS), there are a cylindrical TPC and a large area PID array of time-of-flight (TOF) counters. In addition, there are two small-area single-arm detectors: an electromagnetic calorimeter (Photon Spectrometer, PHOS) and an array of RICH counters optimized for high-momentum inclusive particle identification (HMPID).

# **1.2 General considerations**

The basic functions of the ITS are:

- determination of the primary vertex and of the secondary vertices necessary for the reconstruction of charm and hyperon decays,

- particle identification and tracking of low-momentum particles,

- improvement of the momentum and angle measurements of the TPC.

#### 1.2.1 Tracking in ALICE

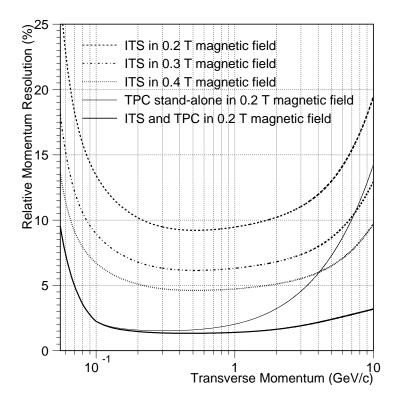

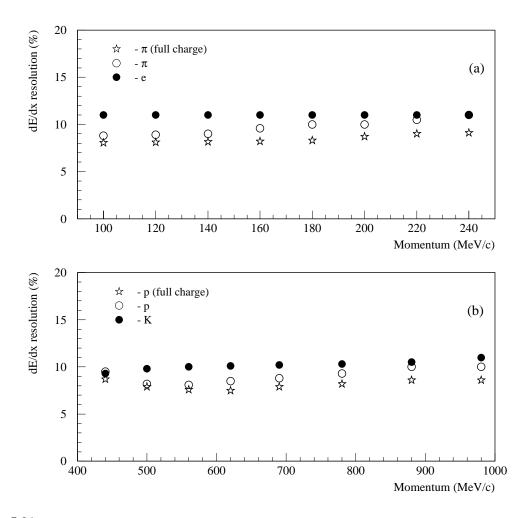

Track finding in heavy-ion collisions at the LHC presents a big challenge, because of the extremely high track density. In order to achieve a high granularity and a good two-track separation ALICE uses threedimensional hit information, wherever feasible, with many points on each track and a weak magnetic field. The ionization density of each track is measured for particle identification. The need for a large number of points on each track has led to the choice of a TPC as the main tracking system. In spite of its drawbacks, concerning speed and data volume, only this device can provide reliable performance for a large volume at up to 8000 charged particles per unit of rapidity. The minimum possible inner radius of the TPC ( $r_{in} \approx 90$  cm) is given by the maximum acceptable hit density. The outer radius ( $r_{out} \approx 250$  cm) is determined by the minimum length required for a dE/dx resolution better than 10%. At smaller radii, and hence larger track densities, tracking is taken over by the ITS.

The ITS consists of six cylindrical layers of silicon detectors. The number and position of the layers are optimized for efficient track finding and impact parameter resolution. In particular, the outer radius is

determined by the track matching with the TPC, and the inner one is the minimum compatible with the radius of the beam pipe (3 cm). The silicon detectors feature the high granularity and excellent spatial precision required.

Because of the high particle density, up to 90 cm<sup>-2</sup>, the four innermost layers ( $r \le 24$  cm) must be truly two-dimensional devices. For this task silicon pixel and silicon drift detectors were chosen. The outer two layers at  $r \approx 45$  cm, where the track densities are below 1 cm<sup>-2</sup>, will be equipped with double-sided silicon microstrip detectors.

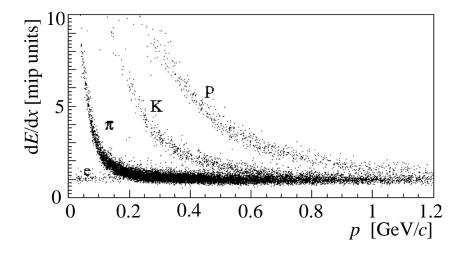

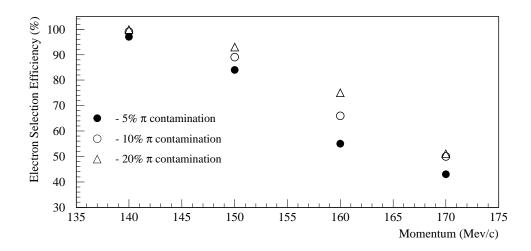

With the exception of the two innermost pixel planes, all layers will have analog readout for particle identification via a dE/dx measurement in the non-relativistic region. This will give the inner tracking system a stand-alone capability as a low- $p_{T}$  particle spectrometer.

#### 1.2.2 Physics of the ITS

The ITS will contribute to the track reconstruction by improving the momentum resolution obtained by the TPC. This will be beneficial for practically all physics topics which will be addressed by the ALICE experiment. The global event features will be studied by measuring the multiplicity distributions and the inclusive particle spectra. For the study of resonance production ( $\rho$ ,  $\omega$  and  $\phi$ ), and, more importantly, the behaviour of the mass and width of these mesons in the dense medium, the momentum resolution is even more important. We have to achieve a mass precision comparable to, or better than, the natural width of the resonances in order to observe changes of their parameters caused by chiral symmetry restoration. Also the mass resolution for heavy states, like D mesons, J/ $\psi$  and Y, will be better, thus improving the signal-to-background ratio in the measurement of the open charm production, and in the study of heavy-quarkonia suppression. Improved momentum resolution will enhance the performance in the observation of another hard phenomenon, the jet production and predicted jet quenching, i.e. the energy loss of partons in strongly interacting dense matter.

The low-momentum particles (below 100 MeV/c) will be detectable only by the ITS. This is of interest in itself, because it widens the momentum range for the measurement of particle spectra, which allows collective effects associated with the large length scales to be studied. In addition, a low- $p_T$  cut-off is essential to suppress the soft  $\gamma$  conversions and the background in the electron-pair spectrum due to Dalitz pairs. Also the PID capabilities of the ITS in the non-relativistic  $(1/\beta^2)$  region will therefore be of great help.

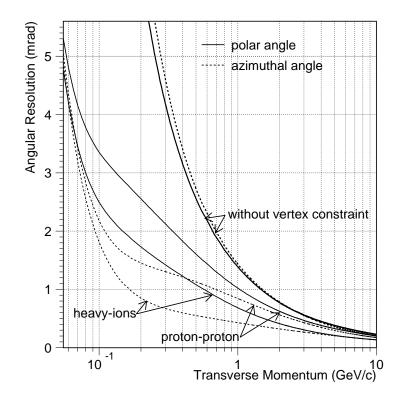

In addition to the improved momentum resolution, which is necessary for the identical particle interferometry, especially at low momenta, the ITS will contribute to this study through an excellent doublehit resolution enabling the separation of tracks with close momenta. In order to be able to study particle correlations in the three components of their relative momenta, and hence to get information about the space-time evolution of the system produced in heavy-ion collisions at the LHC, we need sufficient angular resolution in the measurement of the particle's direction. Two of the three components of the relative momentum (the side and longitudinal ones) are crucially dependent on the precision with which the particle direction is known. The angular resolution is determined by the precise ITS measurements of the primary vertex position and of the first points on the tracks. The particle identification at low momenta will enhance the physics capability by allowing the interferometry of individual particle species as well as the study of non-identical particle correlations, the latter giving access to the emission time of different particles.

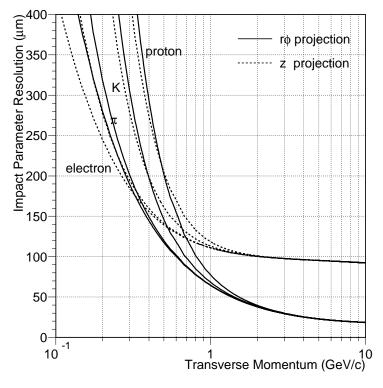

The study of strangeness production is an essential part of the ALICE physics programme. It will allow the level of chemical equilibration and the density of strange quarks in the system to be established. The measurement will be performed by charge kaon identification and hyperon detection, based on the ITS capability to recognize secondary vertices. The observation of multi-strange hyperons ( $\Xi^-$  and  $\Omega^-$ ) is of particular interest, because they are unlikely to be produced during the hadronic rescattering due to the high-energy threshold for their production. In this way we can obtain information about the strangeness density of the earlier stage of the collision. Open charm production in heavy-ion collisions is of great physics interest. Charmed quarks can be produced in the initial hard parton scattering and then only at the very early stages of the collision, while the energy in parton rescattering is above the charm production threshold. The charm yield is not altered later. The excellent performance of the ITS in finding the secondary vertices close to the interaction point gives us the possibility to detect D mesons, by reconstructing the full decay topology.

#### **1.2.3 Design considerations**

The following factors were taken into consideration for the design of the ITS:

- Acceptance: In order to be able to analyse particle ratios,  $p_T$  spectra and particle correlations on an event-by-event basis, the tracking system must have a sufficiently large rapidity acceptance. The rapidity coverage of the tracking system ( $|\eta| < 0.9$ ) is large enough to detect several thousand particles per heavy-ion collision at the currently predicted particle production multiplicity. This rapidity window is also necessary for a good efficiency for detecting the decay of large mass, low transverse momentum particles. An efficient rejection of low-mass Dalitz decays can only be implemented if the detector provides full azimuthal coverage. The first pixel layer has a wider pseudorapidity coverage ( $|\eta| < 1.75$ ) to extend the rapidity coverage of the multiplicity measurement.

- dE/dx measurement: The ITS contributes to particle identification through the measurement of specific energy loss. To apply a truncated-mean method, a minimum of four measurements are necessary, so four out of the six planes need analog readout. As explained in detail in Section 3.3.2, we require the dynamic range of the analog readout to be large enough to provide dE/dx information for low-momentum, highly ionizing particles, down to the minimum momentum for which the tracks have a reasonable (> 20%) reconstruction probability.

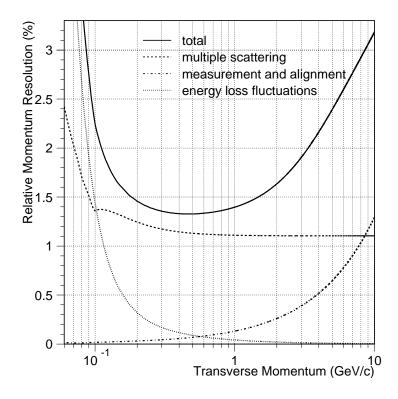

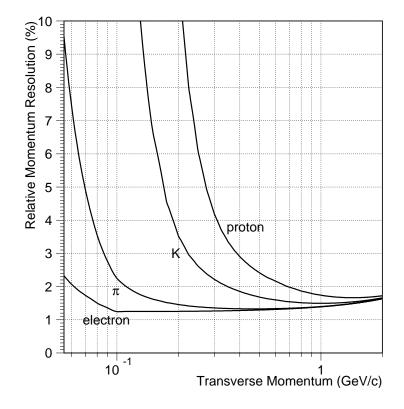

- **Material budget:** The momentum and impact parameter resolution for particles with small transverse momenta are dominated by multiple scattering effects in any existing tracking detector. Therefore the amount of material in the active volume has to be reduced as much as possible. However, the thickness of silicon detectors used to measure ionization densities must be approximately  $300 \mu$ m to guarantee the required signal-to-noise ratio. In addition the detectors must overlap in order to reach full coverage within the acceptance window. Taking also into account the incidence angles of tracks the detectors represent a thickness of 0.4% of  $X_0$ . The aim set in the ALICE technical proposal was to reduce the thickness of the additional material in the active volume, i.e. electronics, cabling, support structure and cooling system, to a comparable effective thickness. The current design tries to meet this challenge. As shown in Chapter 5, the resulting relative momentum resolution is better than 2% for pion momenta between 100 MeV/c and 3 GeV/c.

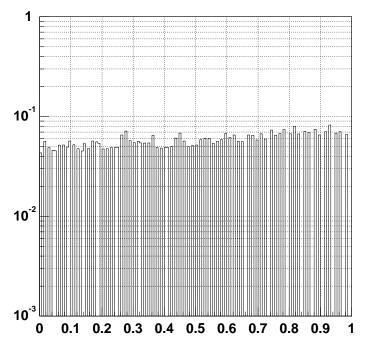

- **Spatial precision and granularity:** The granularity of the detectors in the ITS is dictated by the track densities expected. The system is designed for a maximum track density of 8000 tracks per unit of rapidity, the upper limit of the current theoretical predictions. Therefore up to 15 000 tracks will have to be detected simultaneously in the ITS. Keeping the occupancy of the system at the level of a few per cent requires several million effective cells in each layer of the ITS.

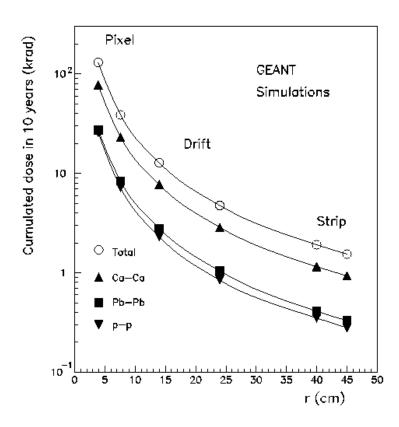

The resolution of the impact parameter measurement is determined by the spatial resolution of the ITS detectors. For charmed particles the impact parameter resolution must be better than 100  $\mu$ m in the  $r\varphi$  direction. Therefore the ITS detectors have a spatial resolution of the order of a few tens of  $\mu$ m, with the best precision (12  $\mu$ m) for the detectors closest to the primary vertex. In addition, for momenta larger than 3 GeV/*c*, relevant for the detection of the decay products of charmed mesons and high-mass quarkonia, the spatial precision of the ITS becomes an essential element of the momentum resolution. This requirement is met by all layers of the ITS with a point

| Layer | Detector |      | Cumulated dose | Neutron fluence $(10^{11} \text{ cm}^{-2})$ |

|-------|----------|------|----------------|---------------------------------------------|

|       |          | (cm) | (krad)         | (10 cm)                                     |

| 1     | pixel    | 4    | 130            | 3.2                                         |

| 2     | pixel    | 7    | 39             | 3.1                                         |

| 3     | drift    | 15   | 13             | 3.5                                         |

| 4     | drift    | 24   | 5              | 3.3                                         |

| 5     | strip    | 39   | 2              | 3.7                                         |

| 6     | strip    | 44   | 2              | 3.3                                         |

**Table 1.1:** Radiation dose and neutron fluence for each of the ITS detector layers, calculated for ten years of operation, including pp and Ca–Ca runs.

resolution in the bending plane about one order of magnitude better than that of the TPC, which in turn provides many more points.

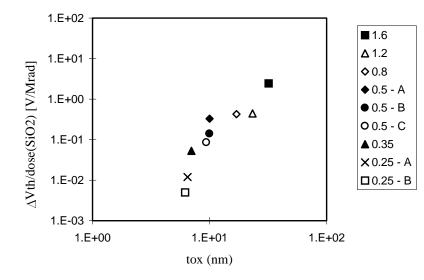

- **Radiation levels:** The ionizing radiation dose received by the detector components was calculated using Monte Carlo techniques based on HIJING and GEANT. The total dose received during the lifetime of the experiment varies from a few krad for the outer parts of the ITS to about 150 krad for the inner parts as shown in Table 1.1. Detailed calculations can be found in Chapter 5 and in Ref. [2]. Each of the sub-detectors is designed to withstand the ionizing radiation doses expected during ten years of operation. The neutron fluence is approximately  $3 \times 10^{11}$  cm<sup>-2</sup> throughout the ITS, which does not cause significant damage to the detectors or the associated electronics. Where necessary, the components used in the ITS design were tested for their radiation hardness up to the expected doses.

- **Readout rate:** The ALICE system will be used in two basically different readout configurations, operated simultaneously with two different triggers. The centrality trigger activates the readout of the whole of ALICE, in particular all layers of the ITS, while the trigger of the muon arm activates the readout of a subset of fast readout detectors, including the two inner layers of the ITS. Therefore the readout time for the pixel detectors is set at 400  $\mu$ s.

#### **1.2.4 Layout of the ITS**

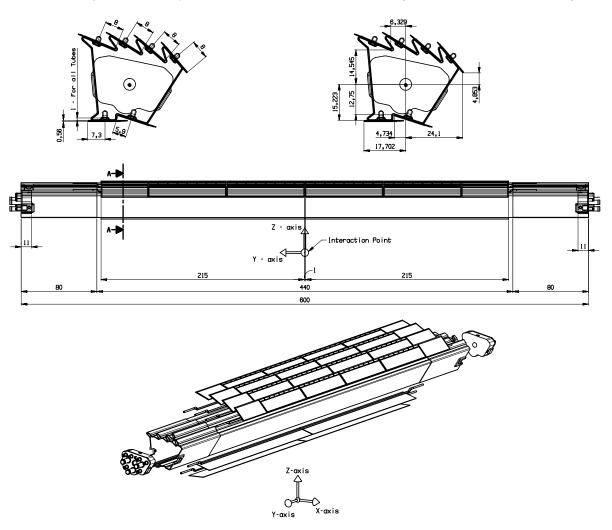

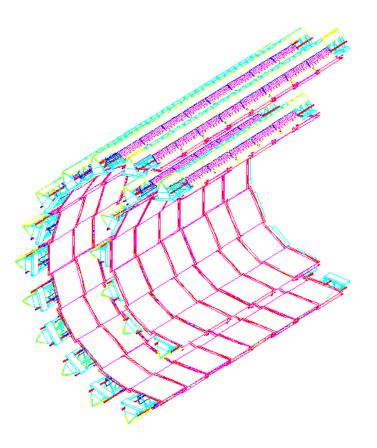

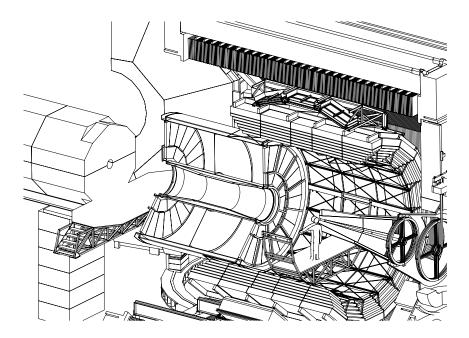

A general view of the ITS is shown in Colour Figs. II and III.

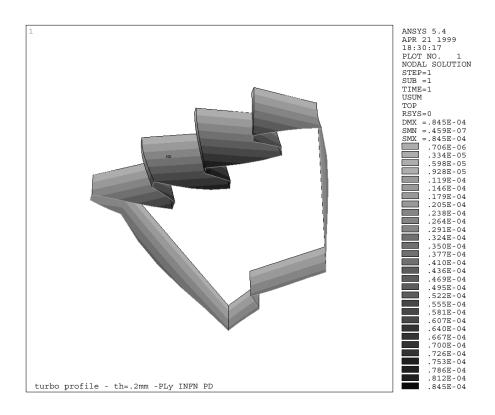

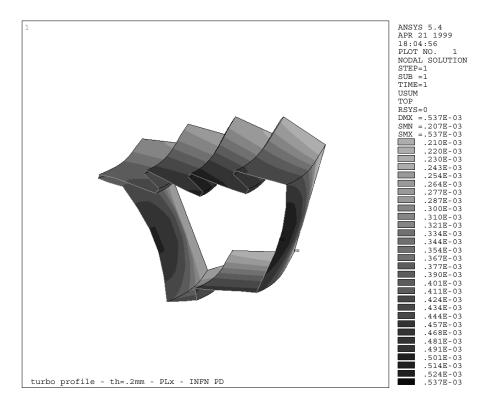

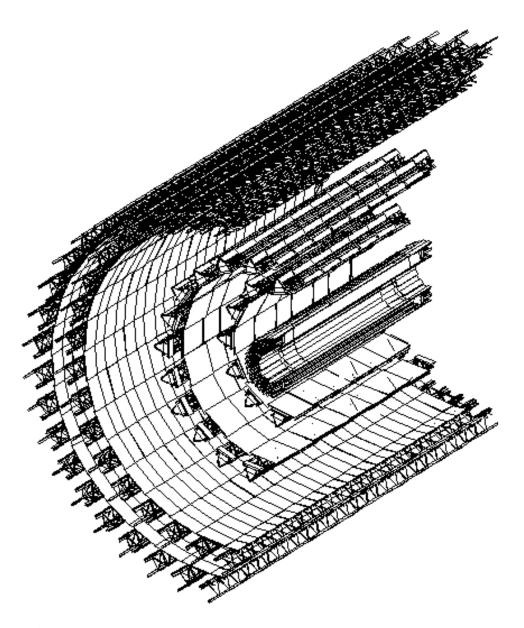

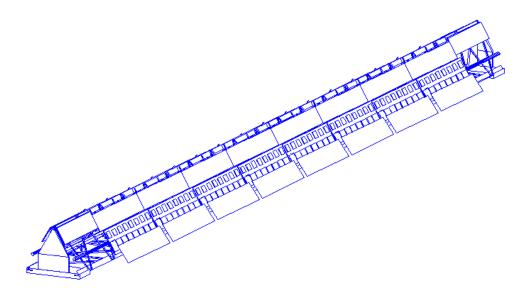

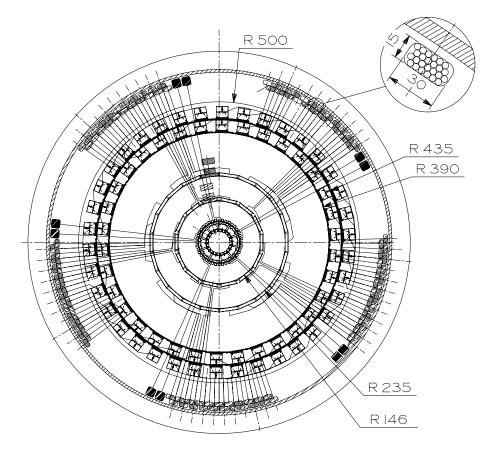

The system consists of six cylindrical layers of coordinate-sensitive detectors, covering the central rapidity region ( $|\eta| \le 0.9$ ) for vertices located within the length of the interaction diamond ( $\pm 1\sigma$ ), i.e. 10.6 cm along the beam direction (z). The detectors and front-end electronics are held by lightweight carbon-fibre structures.

The geometrical dimensions and the technology used in the various layers of the ITS are summarized in Table 1.2.

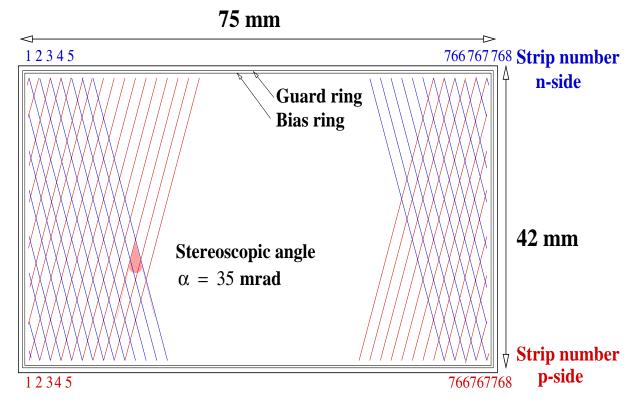

The granularity required for the innermost planes, is achieved with silicon micro-pattern detectors with true two-dimensional readout: Silicon Pixel Detectors (SPD) and Silicon Drift Detectors (SDD). At larger radii, the requirements in terms of granularity are less stringent, therefore double-sided Silicon Strip Detectors (SSD) with a small stereo angle are used. Double-sided microstrips have been selected rather than single-sided ones because they introduce less material in the active volume. In addition they offer the possibility to correlate the pulse height read out from the two sides, thus helping to resolve ambiguities inherent in the use of detectors with projective readout. The main parameters for each of the three detector types: spatial precision, two-track resolution, pixel size, number of channels of an individual detector, total number of electronic channels, dissipated power both in the central region and in the end-caps are shown in Table 1.3.

| Layer | Type                            | <i>r</i> (cm) | $\pm z$ (cm) | Area (m <sup>2</sup> ) | Ladders | Ladders/stave | Det./ladder | Tot. channels |

|-------|---------------------------------|---------------|--------------|------------------------|---------|---------------|-------------|---------------|

| 1     | pixel                           | 4             | 16.5         | 0.09                   | 80      | 4             | 1           | 5 242 880     |

| 2     | pixel                           | 7             | 16.5         | 0.18                   | 160     | 4             | 1           | 10 485 760    |

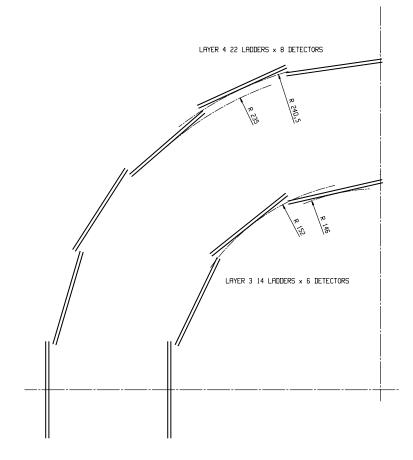

| 3     | drift                           | 14.9          | 22.2         | 0.42                   | 14      | _             | 6           | 43 008        |

| 4     | drift                           | 23.8          | 29.7         | 0.89                   | 22      | _             | 8           | 90112         |

| 5     | strip                           | 39.1          | 45.1         | 2.28                   | 34      | _             | 23          | 1 201 152     |

| 6     | strip                           | 43.6          | 50.8         | 2.88                   | 38      |               | 26          | 1 517 568     |

|       | Total area = $6.74 \text{ m}^2$ |               |              |                        |         |               |             |               |

Table 1.2: Dimensions of the ITS detectors (active areas).

Table 1.3: Parameters of the various detector types. A module represents a single detector chip.

| Parameter                        |           | Silicon Pixel    | Silicon Drift      | Silicon Strip  |

|----------------------------------|-----------|------------------|--------------------|----------------|

| Spatial precision rq             | μm        | 12               | 38                 | 20             |

| Spatial precision z              | $\mu$ m   | 70               | 28                 | 830            |

| Two track resolution rq          | $\mu$ m   | 100              | 200                | 300            |

| Two track resolution z           | $\mu$ m   | 600              | 600                | 2400           |

| Cell size                        | $\mu m^2$ | $50 \times 300$  | $150 \times 300$   | 95 	imes 40000 |

| Active area per module           | $mm^2$    | $13.8 \times 82$ | $72.5 \times 75.3$ | $73 \times 40$ |

| Readout channels per module      |           | 65 536           | $2 \times 256$     | $2 \times 768$ |

| Total number of modules          |           | 240              | 260                | 1770           |

| Total number of readout channels | k         | 15 729           | 133                | 2719           |

| Total number of cells            | Μ         | 15.7             | 34                 | 2.7            |

| Average occupancy (inner layer)  | %         | 1.5              | 2.5                | 4              |

| Average occupancy (outer layer)  | %         | 0.4              | 1.0                | 3.3            |

| Power dissipation in barrel      | W         | 1500-2000        | 510                | 1100           |

| Power dissipation end-caps       | W         |                  | 410                | 1500           |

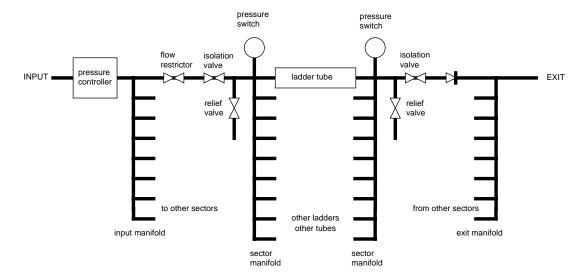

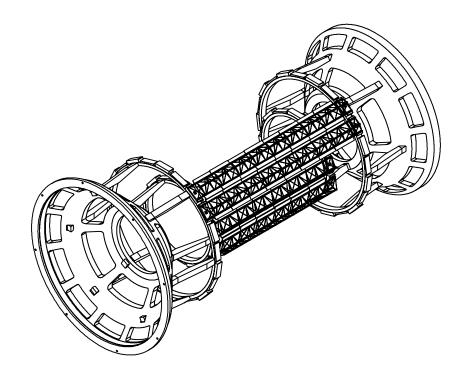

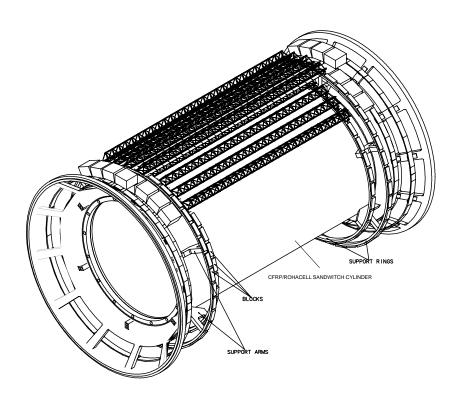

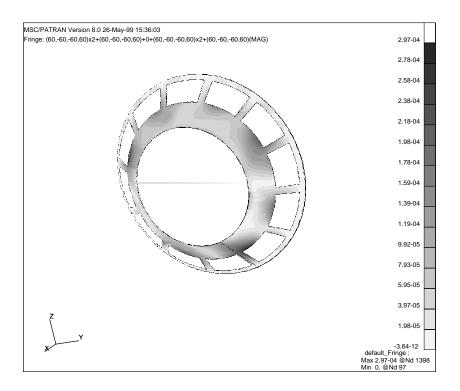

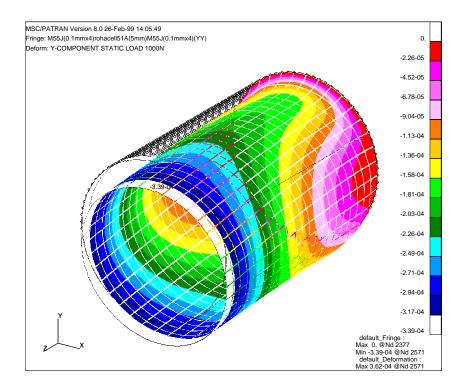

The large number of channels in the layers of the ITS requires a large number of connections from the front-end electronics to the detector and to the readout. The requirement for a minimum of material within the acceptance does not allow the use of conventional copper cables near the active surfaces of the detection system. Therefore TAB bonded aluminium multilayer microcables are used. The detectors and their front-end electronics produce a large amount of heat which has to be removed while keeping a very high degree of temperature stability. In particular, the SDDs are sensitive to temperature variations in the 0.1 °C range. For these reasons, particular care was taken in the design of the cooling system and of the temperature monitoring. A water cooling system at room temperature is the chosen solution for all ITS layers, but the use of other liquid coolants is still being considered. For the temperature monitoring dedicated integrated circuits are mounted on the readout boards and specific calibration devices are integrated in the SDDs. The outer four layers of the ITS detectors are assembled onto a mechanical structure made of two end-cap cones connected by a cylinder placed between the SSD and the SDD layers. Both the cones and the cylinder are made of lightweight sandwiches of carbon-fibre plies and Rohacel<sup>TM</sup>. The carbon-fibre structure includes also the appropriate mechanical links to the TPC and to the SPD layers. The latter are assembled in two half-cylinder structures, specifically designed for safe installation around the beam pipe. The end-cap cones provide the cabling and cooling connection of the six ITS layers with the outside services.

# **1.3** Design of the pixel layers

The two innermost layers of the ITS are fundamental in determining the quality of the vertexing capability of ALICE (determination of the position of the primary vertex, measurement of the impact parameter of secondary tracks from the weak decays of strange, charm and beauty particles). They will operate in a region where the track density exceeds 50 tracks/cm<sup>2</sup>. This calls for the use of a detector of high precision and granularity. In addition, the detector must be able to operate in a relatively high-radiation environment (the total dose received in 10 years by the inner layer is estimated to be of the order of 200 krad).

A silicon detector with a two-dimensional segmentation combines the advantages of unambiguous two-dimensional readout with the geometrical precision, double-hit resolution, speed, simplicity of calibration and ease of alignment characteristics of silicon microstrip detectors. In addition, a high segmentation leads naturally to a low individual diode capacitance, resulting in an excellent signal-to-noise ratio at high speed. These are the main motivations that led to the choice of equipping ALICE with a barrel of two layers of SPDs.

ALICE is expected to run with two types of level 2 (L2, final) triggers (see Section 6.4). The first is based on event centrality. It will run at a frequency of about 40 Hz and it will trigger the readout of the full ALICE detector (central detector and muon arm). For these events, the information provided by the two layers of the SPD barrel will be combined with that coming from the rest of the ITS detectors and from the TPC in the global tracking. The second type of L2 is based on the detection of dimuon pairs in the muon arm. It will run at a frequency of about 1 kHz, and will only trigger the readout of the SPD and of the muon arm. For these events, the information provided by the SPD barrel will be used in a stand-alone mode to provide a determination of the position of the primary interaction vertex (see Chapter 5).

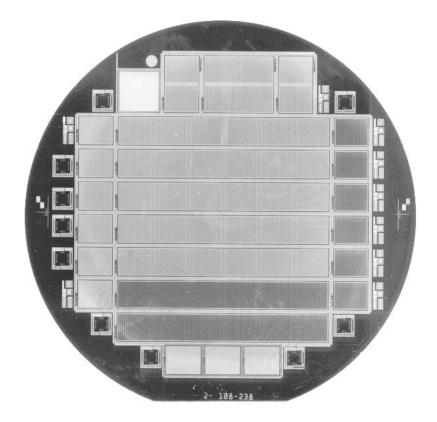

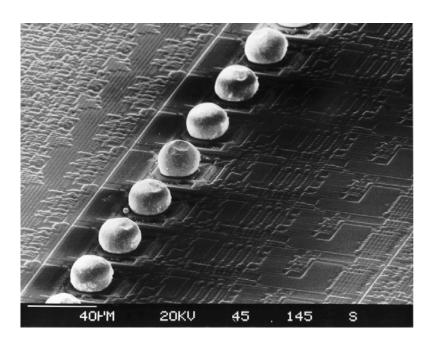

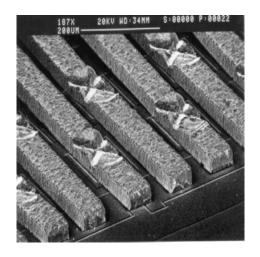

The price to pay for the use of a silicon detector with very high segmentation is a large increase in the number of connections and electronics channels. The production of practical silicon pixel devices has been made possible by the continuous progress in the component density achievable in CMOS microelectronics chips and by the development of fine-pitch surface packaging techniques (flip-chip bonding). The SPD technique was developed at CERN in the framework of a dedicated R&D Collaboration (RD19) led by E. Heijne. A two-dimensional matrix (detector ladder) of reverse-biased silicon detector diodes (typically rectangles of a few tens of  $\mu$ m by a few hundreds of  $\mu$ m) is flip-chip bonded to several front-end chips: Each cell on the detector matrix is connected via a solder ball (sometimes indium is used) to a cell of the same size on a front-end CMOS chip, which contains most of the readout electronics. Usually, the information provided is binary: a threshold is applied to the preamplified and shaped signal, and each cell outputs a logical one if the threshold is exceeded.

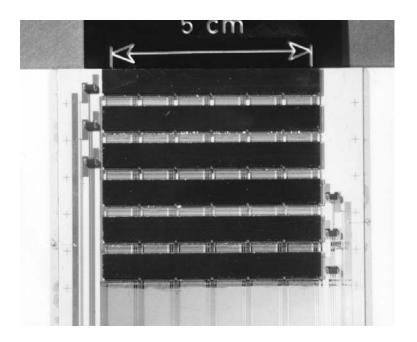

This technique was applied in the development of two generations of SPDs: Omega2 (with cells of  $75 \times 500 \ \mu m^2$ ) and Omega3 (with cells of  $50 \times 500 \ \mu m^2$ ). Several  $5 \times 5 \ cm^2$  planes of SPDs were built using Omega2 and Omega3 ladders. They were first employed in the WA97 experiment at CERN. At present, 7 planes of Omega2 detectors and 6 planes of Omega3 detectors are in use in the Silicon Pixel Telescope of experiment NA57 at CERN, for a total of  $\sim 1.1 \times 10^6$  channels.

Most of the groups currently involved in the ALICE SPD project participated in the RD19 Collaboration and in the WA97 experiment. All of them are participating in the NA57 experiment. The experience we gained in RD19, WA97 and NA57 has been fundamental in the definition of the ALICE SPD project.

Additional experience was gathered with the design and tests of two prototype ALICE test chips, on which we developed and characterized a radiation-tolerant layout technique for deep-submicron CMOS. The application of a system of SPDs in ALICE also imposes other tight constraints. The system should be very lightweight and compact and will be inaccessible during operation, thus requiring a powerful and reliable system of remote control. These issues were also addressed. We have undertaken specific R&D efforts in the area of readout and control, with the development of a fast copper serial data link and of a JTAG accelerator. Similarly, in the area of support and cooling, we have developed prototypes of

lightweight support and cooling structures based on the use of composite materials.

The experience gained from all the R&D efforts mentioned above and the resulting design of the ALICE SPD barrel are described in Chapter 2 of this document. In the remainder of this introductory section, we summarize the main features of the SPD design.

#### **1.3.1** Detector overview

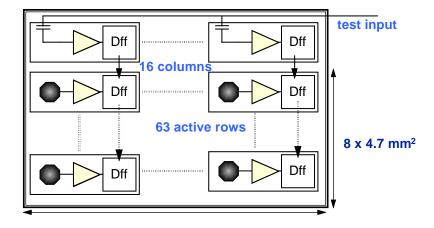

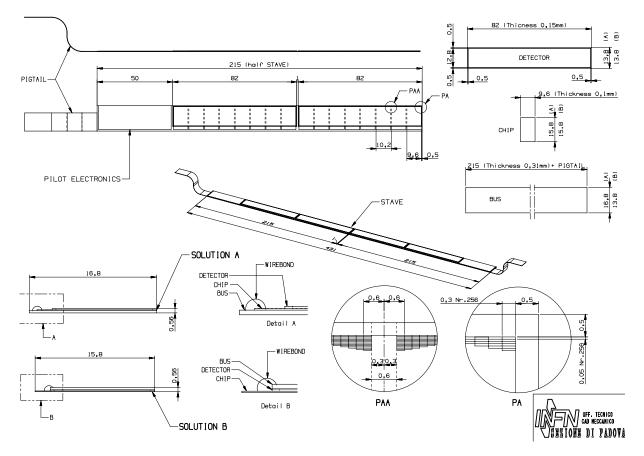

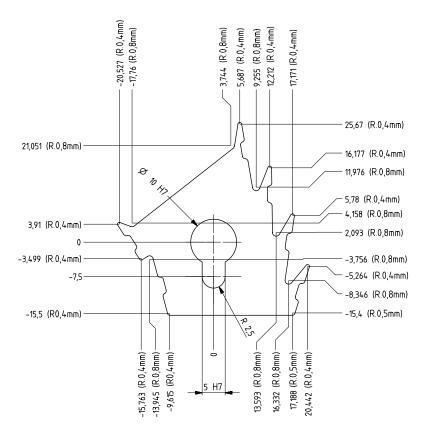

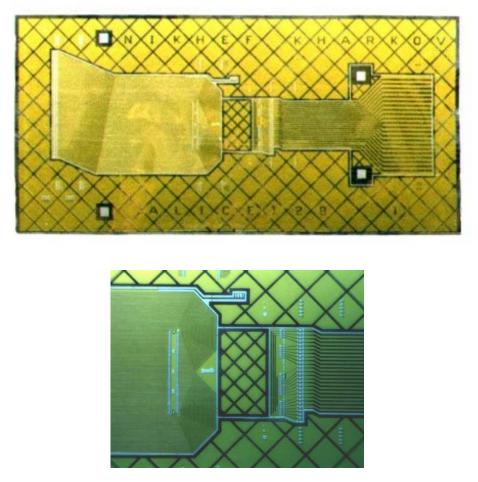

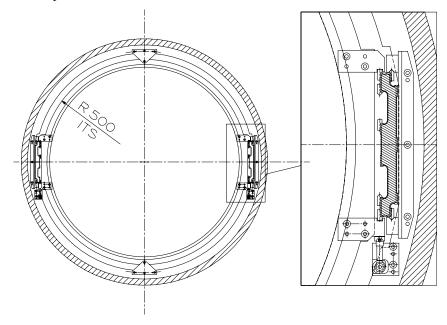

The basic building block of the ALICE SPD is the ladder, consisting of a pixel detector matrix flip-chip bonded to 8 front-end chips. The detector matrix consists of  $256 \times 256$  cells, each measuring 50  $\mu$ m in the  $r\varphi$  direction by 300  $\mu$ m in the z direction. Each detector ladder measures 13.8 mm ( $r\varphi$ ) × 82 mm (z). Each front-end chip contains the electronics for the readout of a submatrix of 256 ( $r\varphi$ ) × 32 (z) detector cells. The detector is 150  $\mu$ m thick and the electronics chip 100  $\mu$ m thick, for a total silicon budget of 250  $\mu$ m.

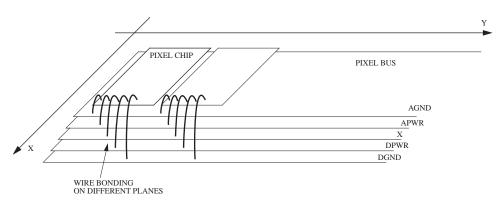

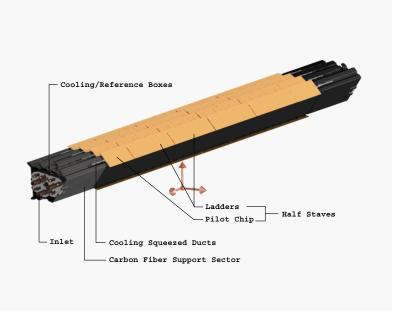

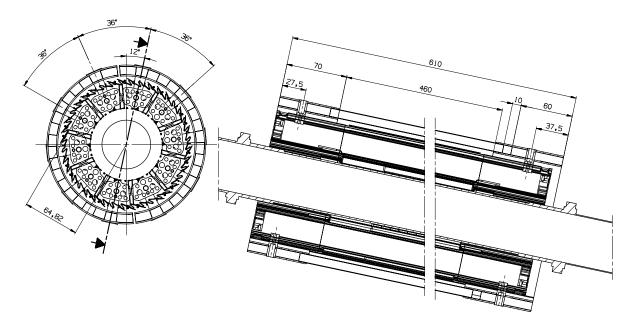

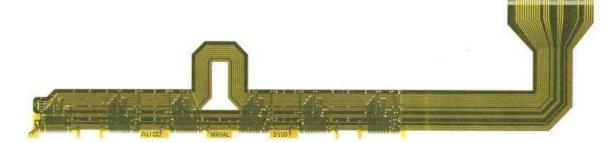

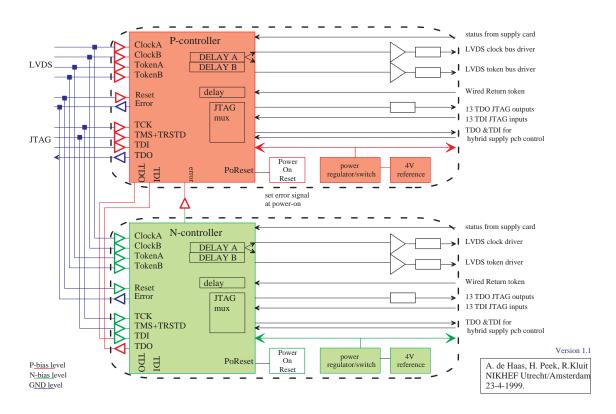

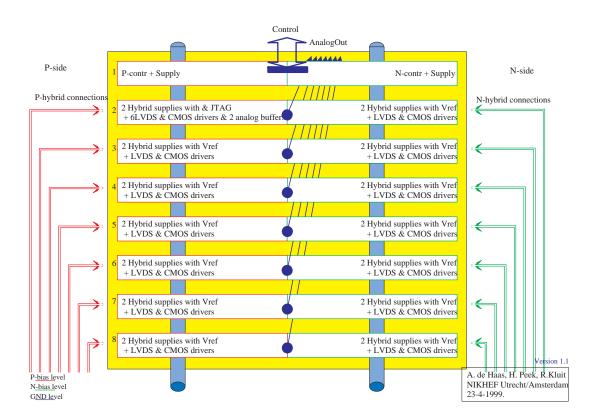

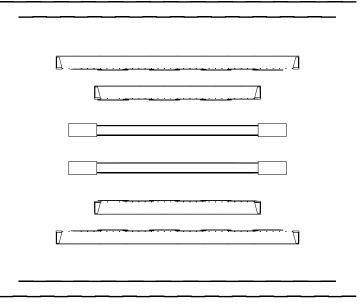

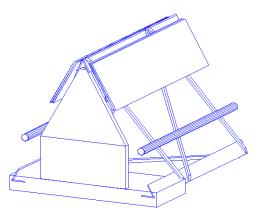

Four ladders are aligned in the *z* direction to form a 33 mm long stave (see figure 2.58 on page 67). They are mounted (glued and wire-bonded) on a multilayer thin carrier (stave bus) which contains the bus and power lines. Two pilot chips located at the extremities of the stave bus perform the readout and control functions and transmit the binary data from the pixel cells to a remote router via a serial copper link.

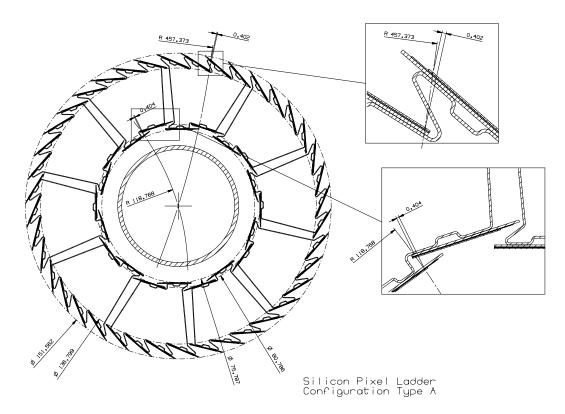

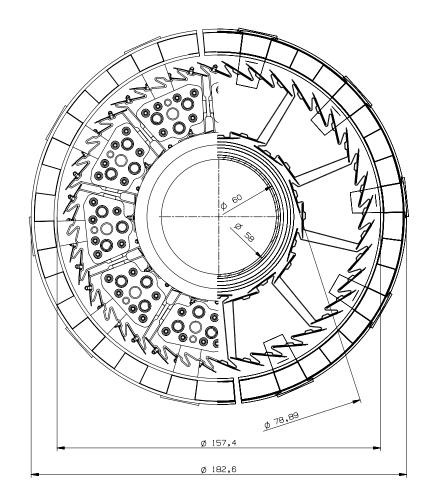

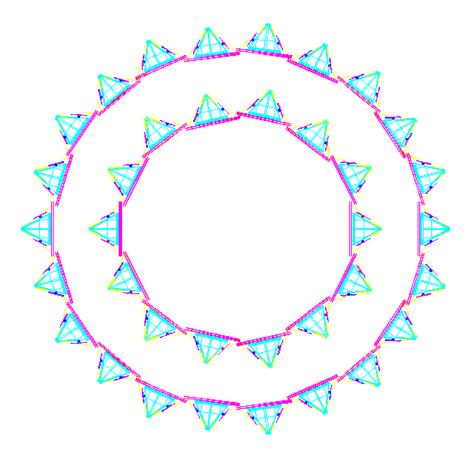

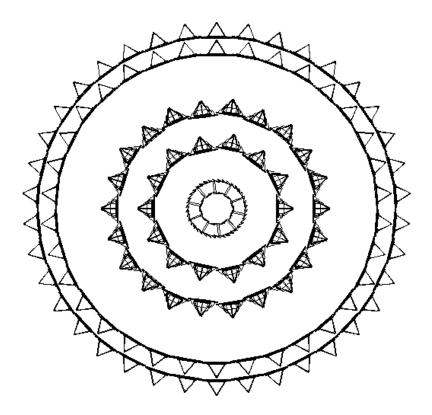

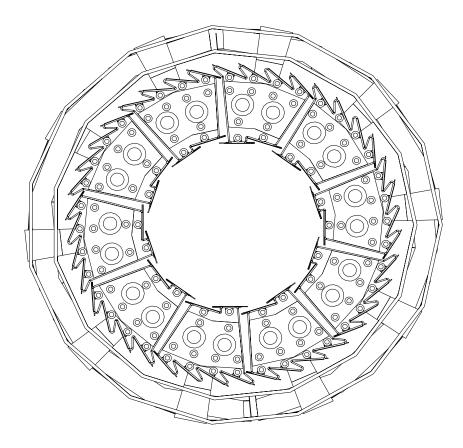

Six staves, two from the inner layer and four from the outer layer, are mounted on a carbon fibre support and cooling sector (see figure 2.59 on page 68). Ten such sectors are then mounted together around the beam pipe to close the full barrel. In total, there will be 60 staves, 240 ladders, 1920 chips,  $15.7 \times 10^6$  cells. The staves of the inner (outer) SPD layer are located at an average distance of 4 cm (7 cm) from the beam axis.

The complete system is expected to generate between 1.5 and 2 kW of thermal power. The sectors are equipped with cooling vessels running underneath the staves (one per stave). Cooling collectors are placed at the two extremities of the sectors. Depending on the side, they distribute the cooling fluid to the cooling vessels or collect it from them. In order to avoid radiation of heat towards the SDD layers, which are very sensitive to temperature, an Al-coated carbon-fibre external shield surrounds the SPD barrel.

The average material traversed by a straight track perpendicular to the beam line crossing the SPD barrel corresponds to about 1.7% of  $X_0$ . The external shield should contribute on average an additional 0.25% of  $X_0$ .

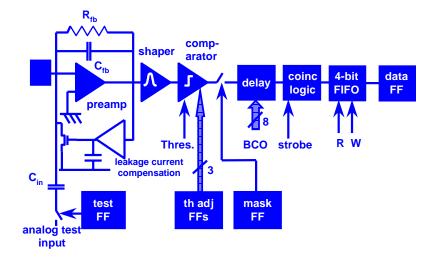

#### 1.3.2 Front-end electronics

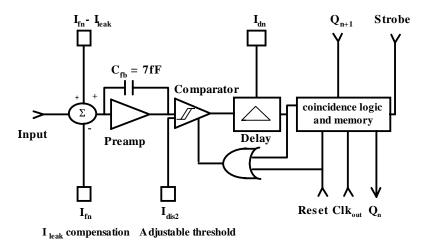

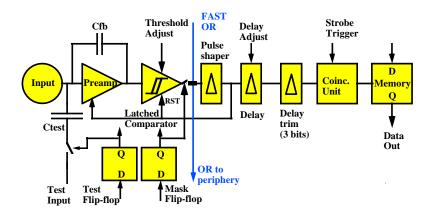

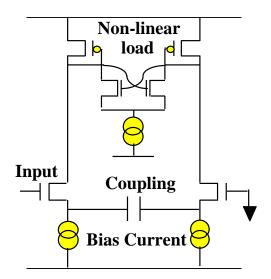

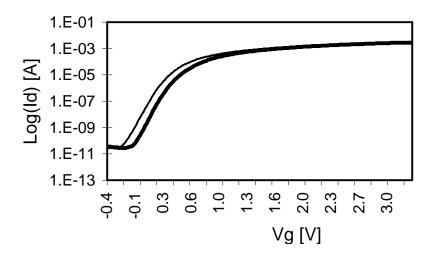

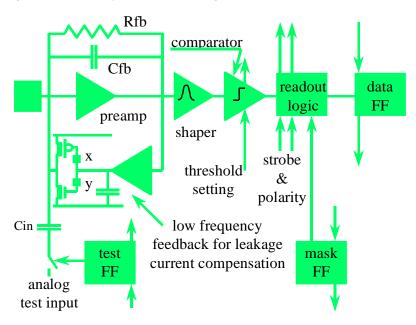

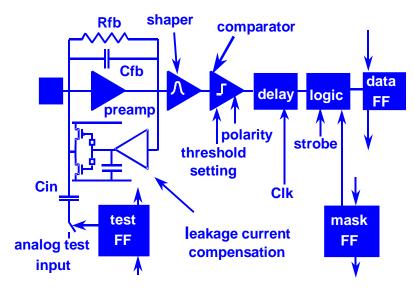

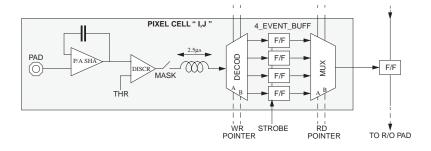

Each front-end chip contains the electronics for the readout of 8192 detector cells. Each cell measures 50  $\mu$ m × 300  $\mu$ m. It contains a mixture of analog and digital electronics.

A preamplifier-shaper with leakage current compensation is followed by a discriminator with an individual threshold fine tuning. A signal above threshold results in a logical one which is propagated through a delay line during the latency time of the level (L1) trigger (5.5  $\mu$ s).

A four-hit deep front-end buffer on each cell allows the event arrival times to be derandomized. When the strobe arrives, the logical level present at the end of the delay line is stored in the first available buffer location.

The periphery contains the JTAG control and biasing circuitry, and the pads for wire-bonding to the stave bus.

The front-end chips are being designed with a radiation-tolerant layout technique (enclosed gate geometry) in standard 0.25  $\mu$ m CMOS. As discussed in Section 2.1, this technique has proven to be tolerant up to at least a few tens of Mrad.

The main requirements for the ALICE SPD front-end chip are listed in Table 1.4.

| Cell size                          | $50 \mu\mathrm{m} (r\mathrm{\phi}) \times 300 \mu\mathrm{m} (z)$ |

|------------------------------------|------------------------------------------------------------------|

| Number of cells                    | 256 ( $r\phi$ ) × 32 ( $z$ )                                     |

| Minimum threshold                  | below 2000 e                                                     |

| Threshold uniformity               | 200 е                                                            |

| Strobe (L1) latency                | up to 10 <i>µ</i> s                                              |

| Strobe duration                    | 200 ns                                                           |

| Clock frequency                    | 10 MHz                                                           |

| Radiation tolerance                | 500 krad                                                         |

| Individual cell mask               | yes                                                              |

| Digital bias adjust (on-chip DACs) | yes                                                              |

| JTAG controls                      | yes                                                              |

**Table 1.4:** Main requirements for the ALICE SPD front-end chip

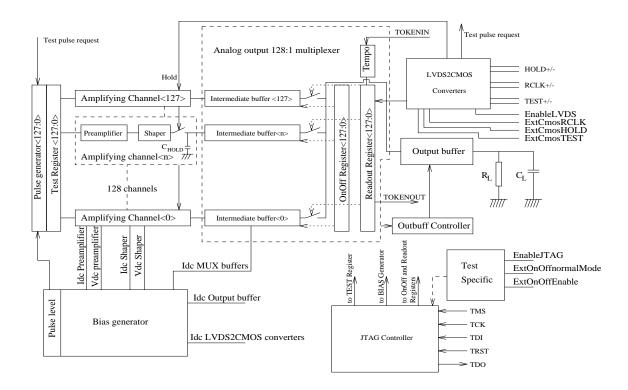

#### 1.3.3 Readout and control

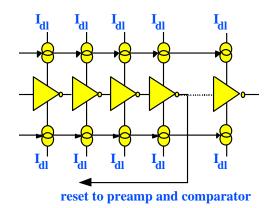

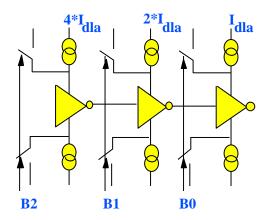

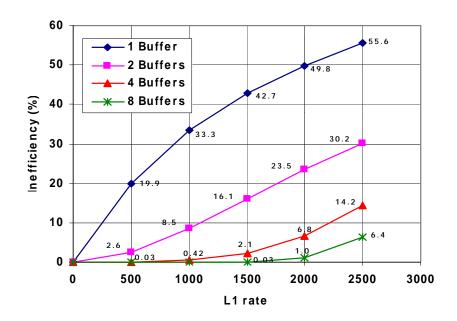

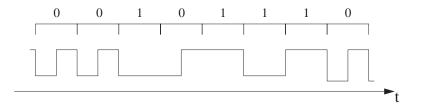

At L2 (latency of 100  $\mu$ s), the data contained in the front-end buffer locations corresponding to the first (oldest) strobe are loaded onto the output shift registers. Then, for each chip, the data from the 256 rows of cells are shifted out during 256 cycles of a 10 MHz clock. At each cycle, a 32-bit word containing the hit pattern from one chip row is output on the 32-bit stave data bus, where it is read out by the pilot chip mounted at the end of the carrier. A full front-end chip is read out in about 25  $\mu$ s. The 16 chips of two ladders (one half-stave) are read out sequentially in a total time of about 400  $\mu$ s. The 120 half-staves are read out in parallel. The dead time introduced by the readout of the SPD is estimated to be below 10% in the worst case, corresponding to ALICE running with Ca–Ca beams at high luminosity, with an L1 rate of 2.5 kHz.

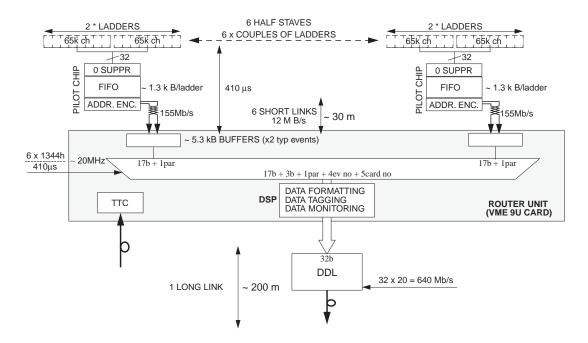

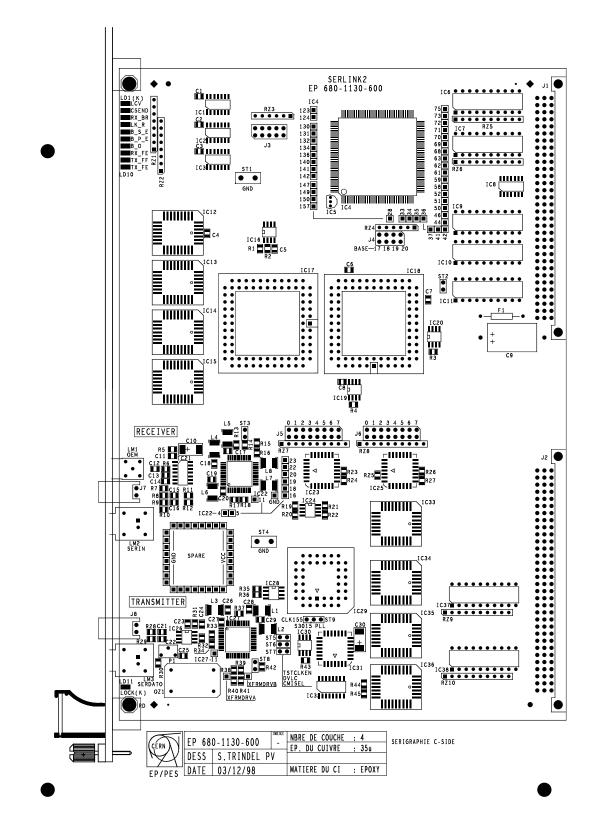

On the pilot chip, data are zero-suppressed, reformatted and sent through a 40 m long copper serial link to a router, where a second level of multiplexing is performed before the data are finally shipped to the DAQ on 20 DDL optical links.

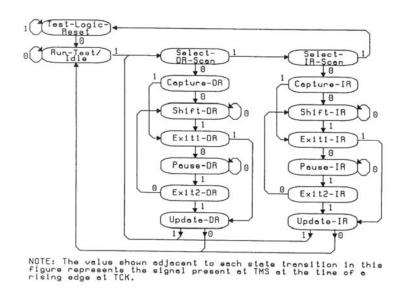

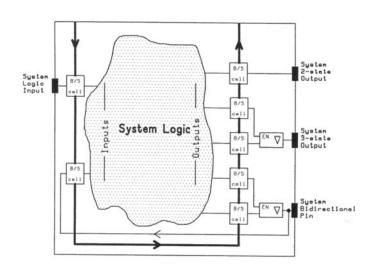

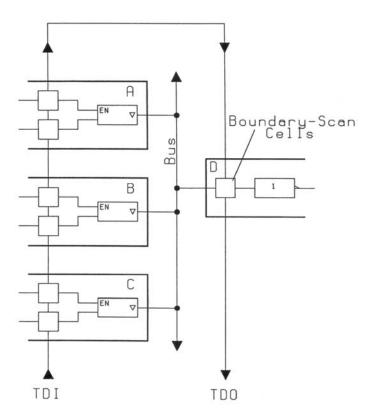

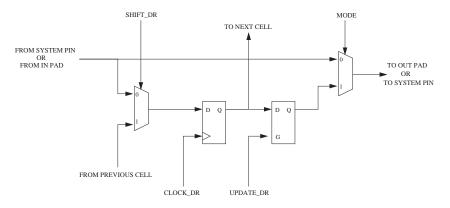

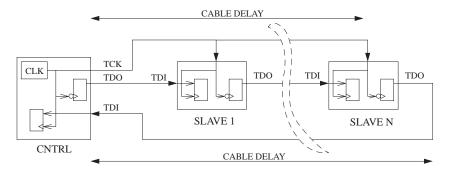

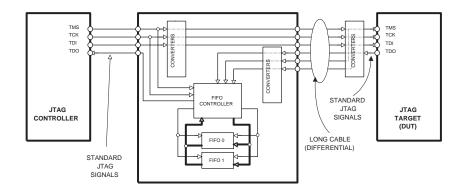

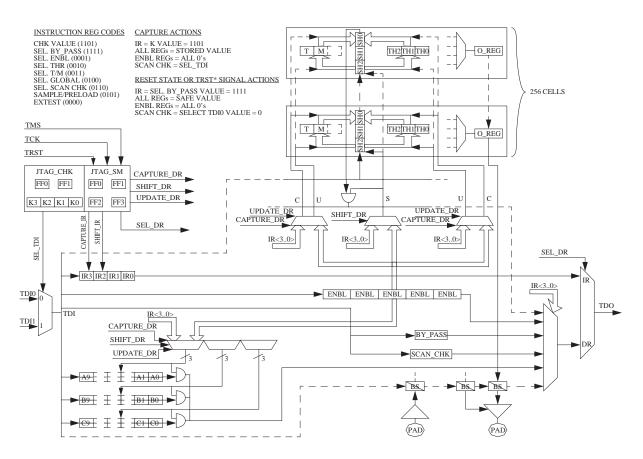

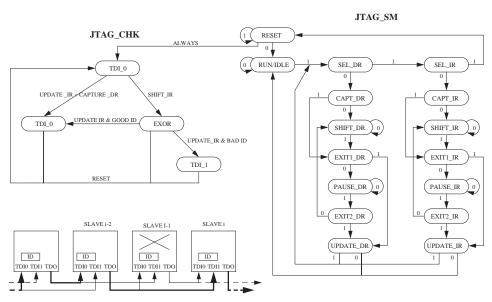

The test and control system, down to the loading of the parameters on the front-end chip, is implemented using the JTAG protocol.

Like the front-end chip, the pilot chip will be realized in enclosed gate 0.25  $\mu$ m CMOS.

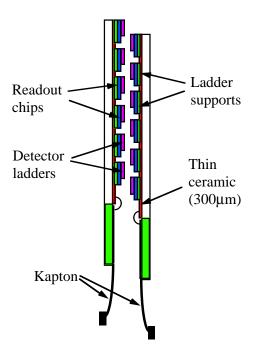

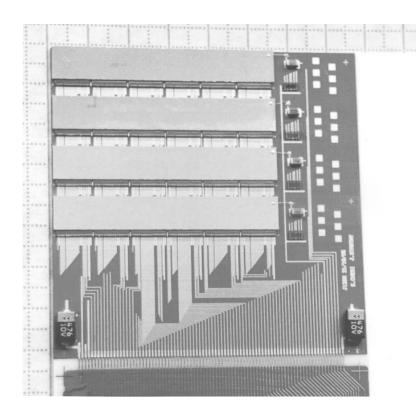

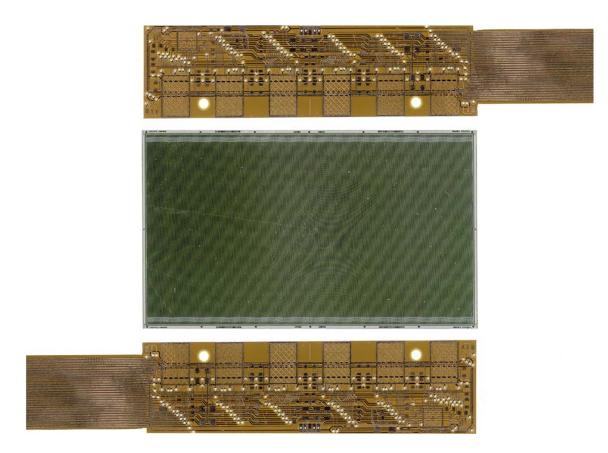

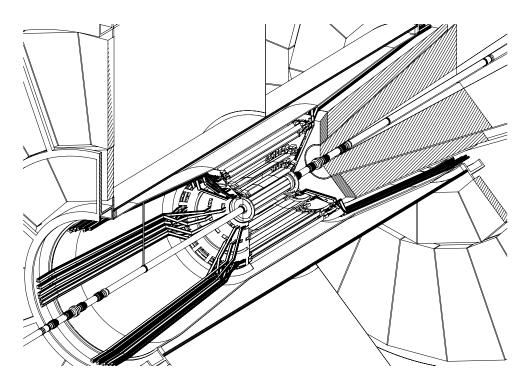

# **1.4 Design of the drift layers**

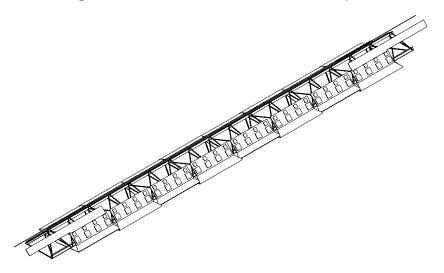

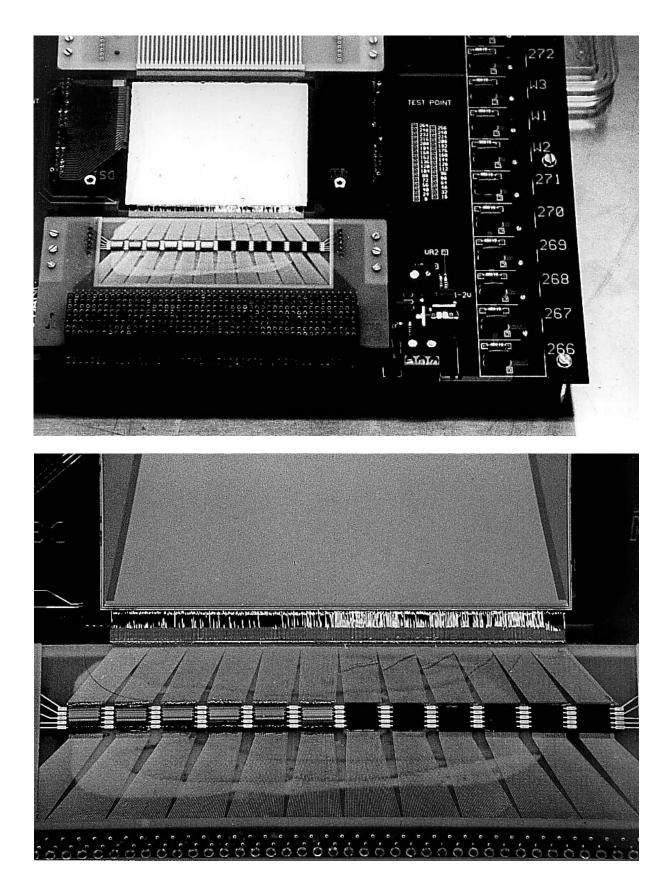

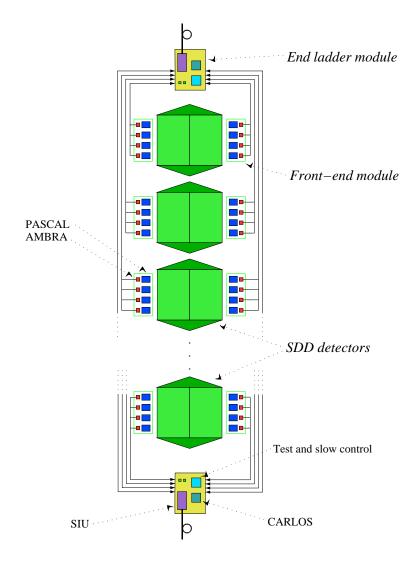

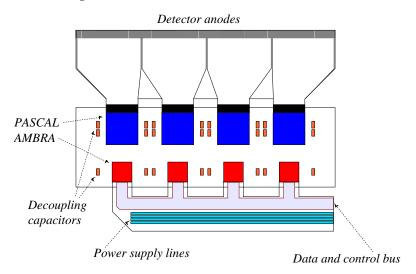

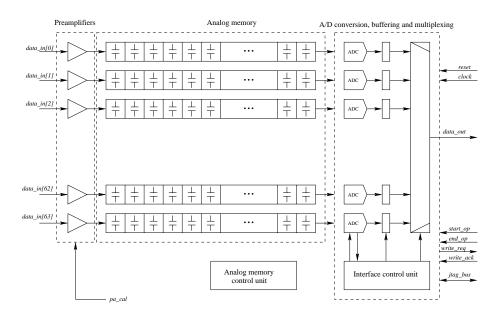

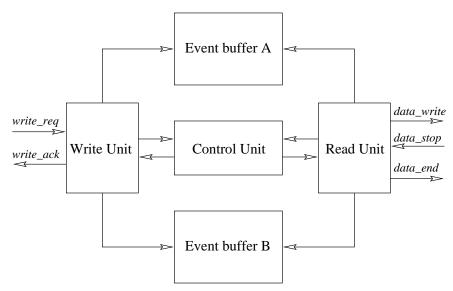

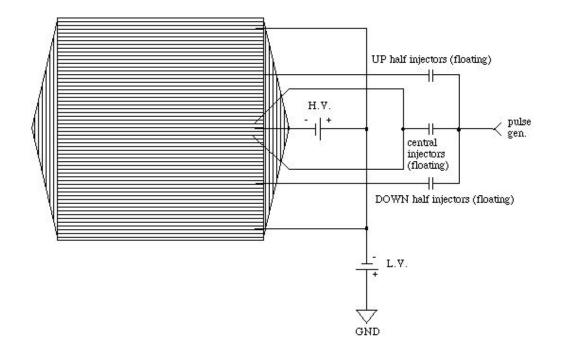

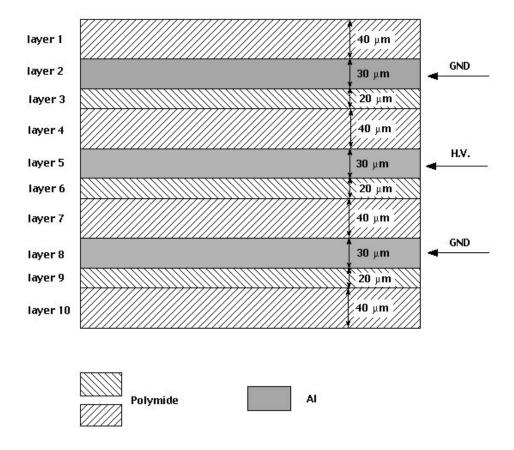

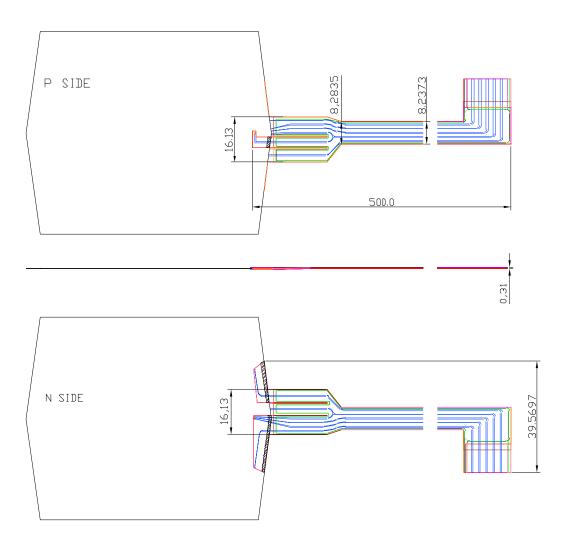

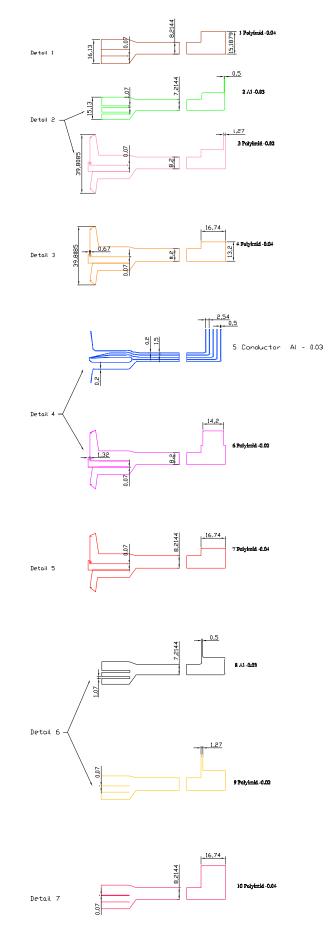

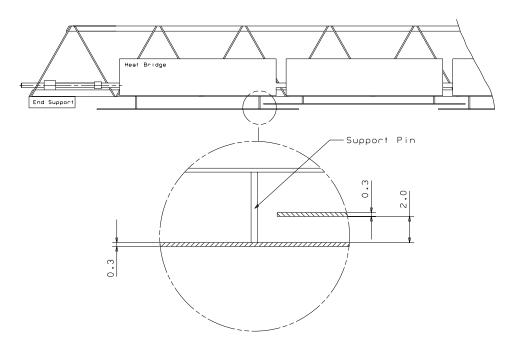

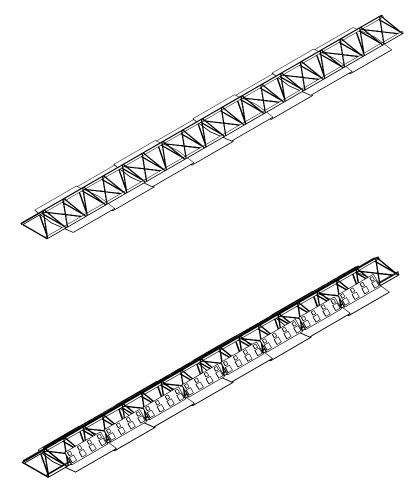

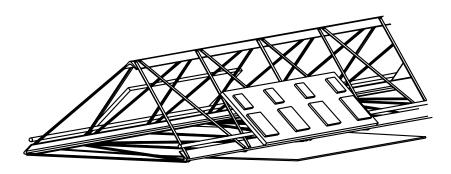

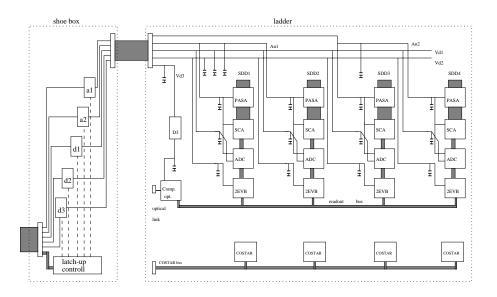

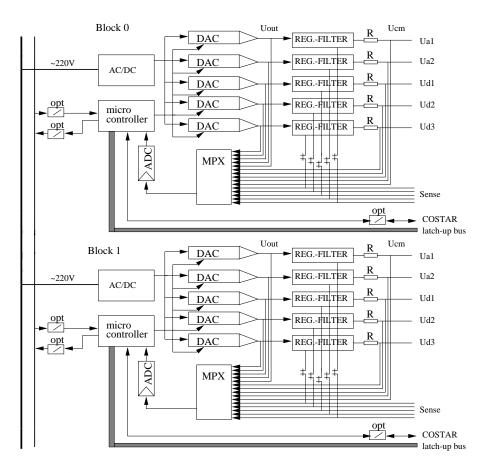

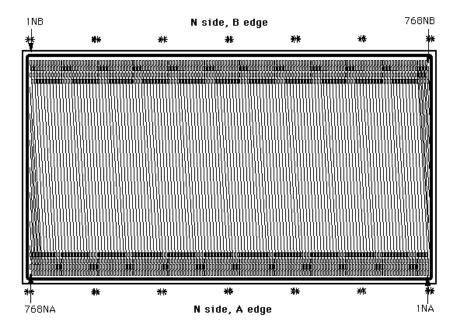

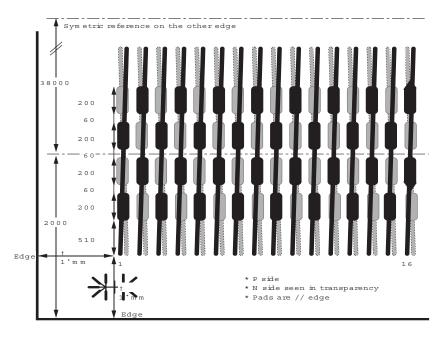

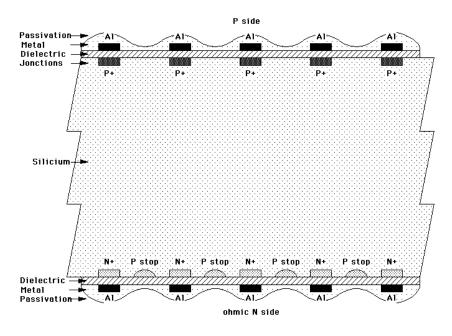

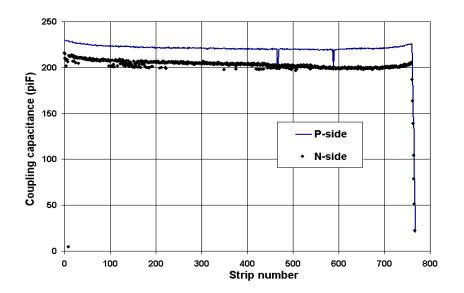

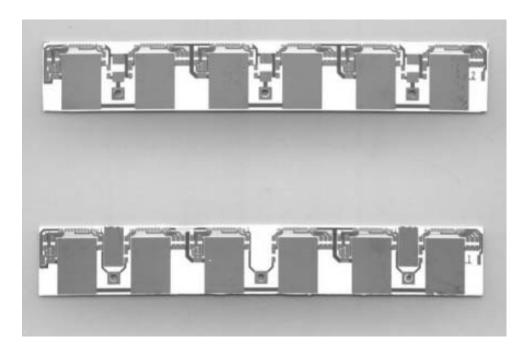

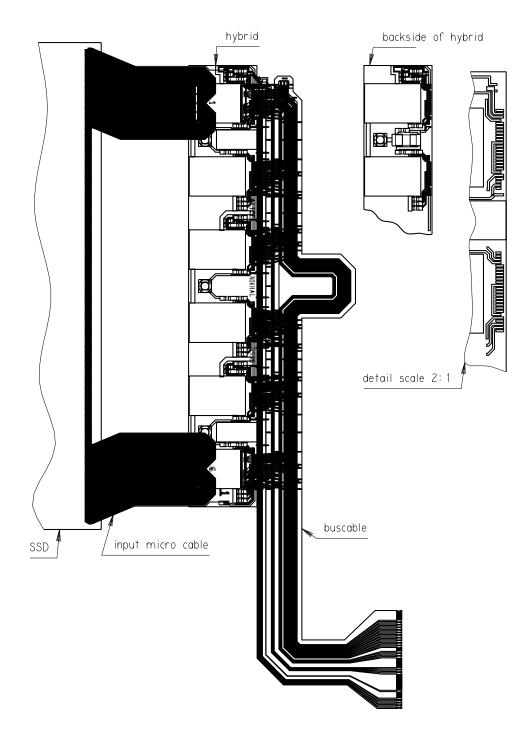

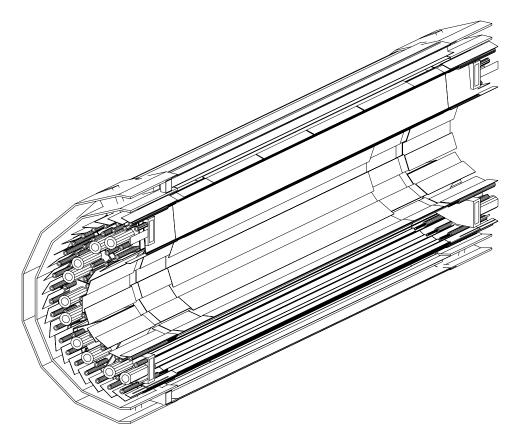

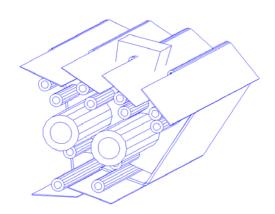

SDDs have been selected to equip the two intermediate layers of the ITS, since they couple a very good multi-track capability with dE/dx information. As mentioned before, at least three measured samples per track, and therefore at least four layers carrying dE/dx information are needed. The SDDs,  $7.25 \times 7.53$  cm<sup>2</sup> active area each (Colour Fig. XII), will be mounted on linear structures called ladders, each holding six detectors for layer 3, and eight detectors for layer 4. The layers will sit at the average radius of 14.9 and 23.8 cm and will be composed of 14 and 22 ladders respectively. The front-end electronics will be mounted on rigid heat-exchanging hybrids, which in turn will be connected onto cooling pipes running along the ladder structure. The connections between the detectors and the front-end electronics, and between both and the ends of the ladder will be assured with flexible Al microcables, Tape Automatic Bonded (TAB), which will carry both data and power supply lines. The front-end electronics will consist of two integrated circuits. The first one, named PASCAL, performs the preamplification of the signals, the analog storage of them at a sampling frequency of about 40 MHz for the about 5.4  $\mu$ s duration of the drift in the detectors, and the analog-to-digital conversion. The second integrated circuit, AMBRA, is a digital two-event buffer which allows data derandomization and transmission to the end-

of-ladder module. This module serves one half-ladder (i.e. three or four detectors) and implements the data compression, the interface with the optical fibre channel to the DAQ system, the clock and trigger distribution and the fine voltage regulation. A slow control system based on the JTAG protocol takes care of the monitoring of voltages and currents, while a second JTAG link, DAQ controlled, is devoted to the configuration and calibration procedures. Each detector will be first assembled together with its front-end electronics and high-voltage connections as a unit, hereafter referred to as a *module*, which will be fully tested before it is mounted on the ladder.

#### 1.4.1 The SDDs

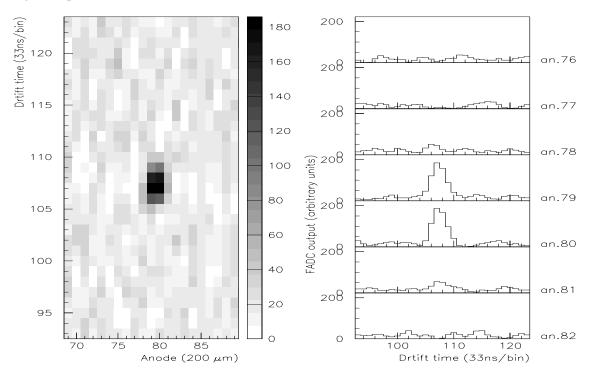

SDDs, like gaseous drift detectors, exploit the measurement of the transport time of the charge deposited by a traversing particle to localize the impact point in one of the dimensions, thus enhancing resolution and multi-track capability at the expense of speed. They are therefore well suited to this experiment in which very high particle multiplicities are coupled with relatively low event rates.

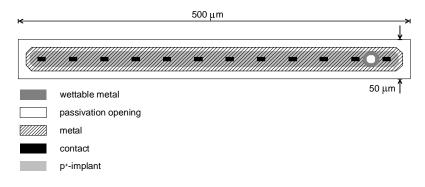

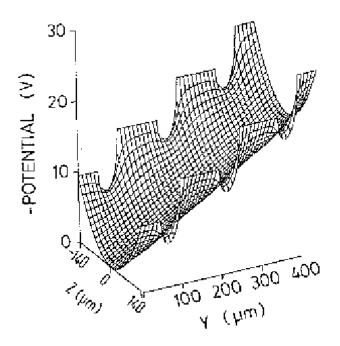

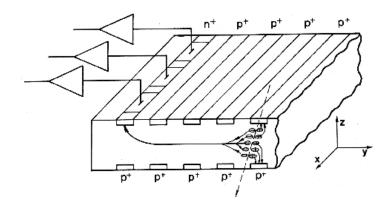

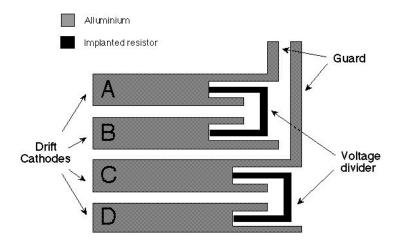

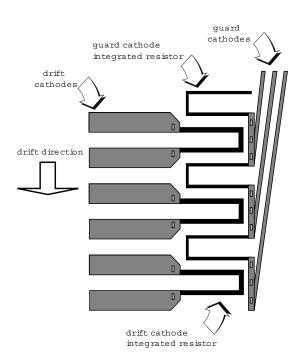

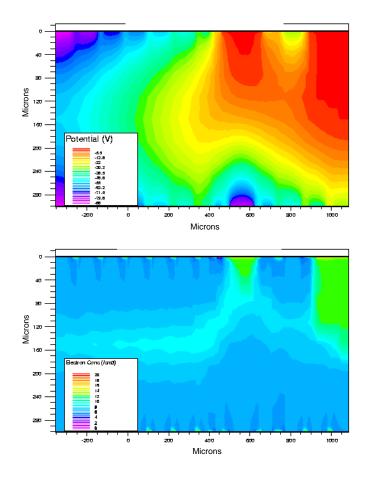

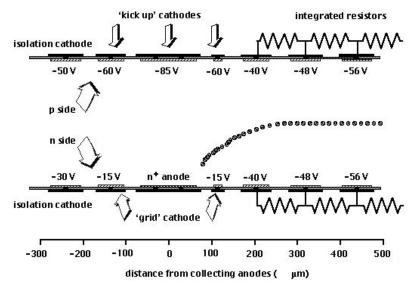

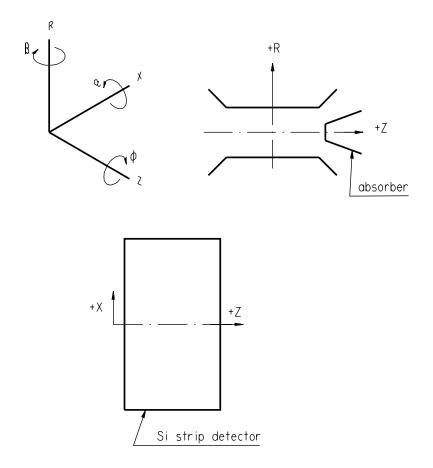

A linear SDD, shown schematically in Fig. 3.5 on page 87, has a series of parallel, implanted  $p^+$  field strips, connected to a voltage divider on both surfaces of the high-resistivity n-type silicon wafer. The voltage divider is integrated on the detector substrate itself. The field strips provide the bias voltage to fully deplete the volume of the detector and they generate an electrostatic field parallel to the wafer surface, thus creating a drift region (see Fig. 3.4 on page 86).

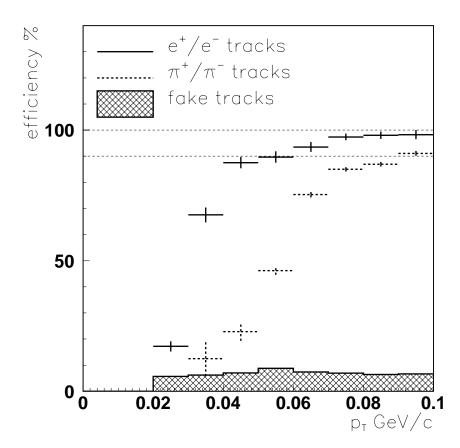

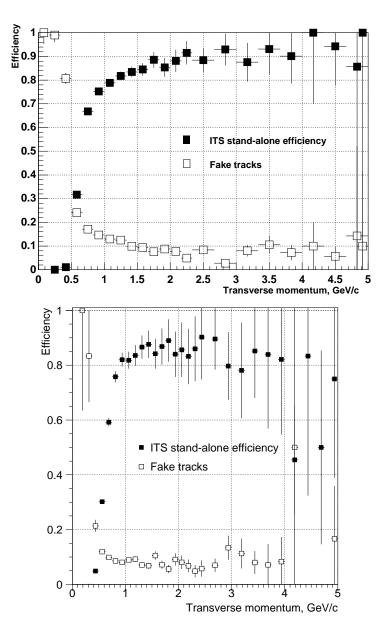

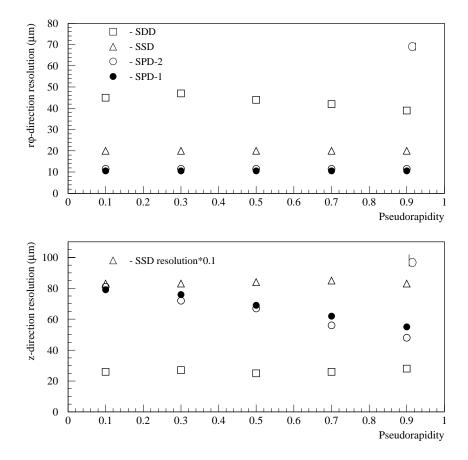

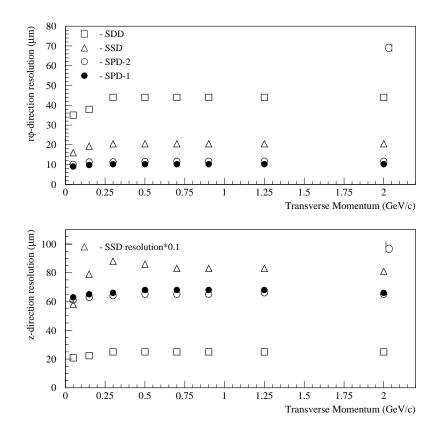

Electron-hole pairs are created by the charged particles crossing the detector. The holes are collected by the nearest  $p^+$  electrode, while the electrons are focused into the middle plane of the detector and driven by the drift field towards the edge of the detector where they are collected by an array of anodes composed of  $n^+$  pads. The small size of the anodes, and hence their small capacitance ( $\approx 50$  fF), imply low noise and good energy resolution.